編集部

2021年3月号 特集サポート

FPGA開発ツールの使い方

~インテル製FPGAを使う場合~

~インテル製FPGAを使う場合~

◆ FPGA開発ツール“QuartusPrime”のセットアップ

●アカウント取得

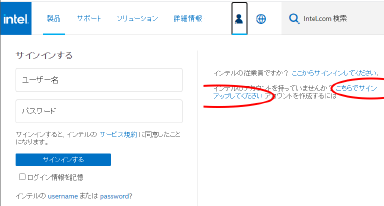

初めてインテル社のツールを使う場合は、アカウントの登録が必要です。インテル社のFPGAのWebサイトにアクセスし、右上にある人間型のアイコンをクリックします。

図1 インテル社のWebサイトの右上

すでにアカウントをお持ちの場合は、登録したメールアドレスとパスワードを入力して「サインイン」してください。アカウントを作成する場合は「こちらでサインアップしてください」をクリックをクリックします。

図2 インテル社のサインイン画面

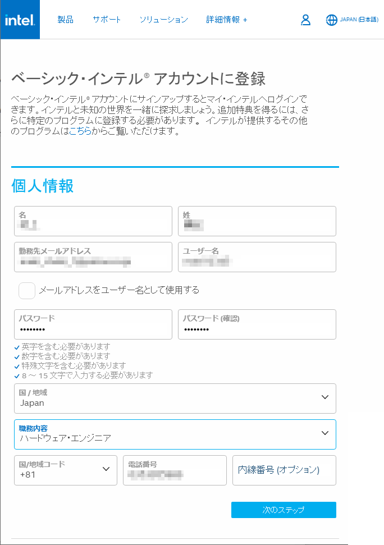

アカウント作成画面では、登録する名前やメールアドレスを入力します。ユーザー名はすでに登録されている名前の場合は警告が出るので、別の名前を登録します。パスワードは英数字と記号を含み、最低8文字が必要です。必要事項の入力が完了すると、右下の「次のステップ」が選択可能になるので、それをクリックします。

図3 アカウント作成画面

アカウント情報を入力すると、アカウント送信画面になるので、「送信」をクリックします。

図4 アカウント送信画面

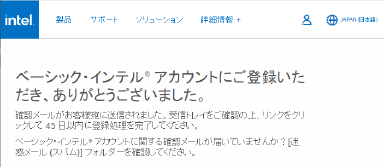

しばらくすると、アカウント登録作業画面が表示されます。

図5 アカウント登録作業完了画面

と同時に、登録したメールアアドレスにメールが送信されます。

What you need to do

Please verify your e-mail address by clicking this link or by copying the URL into your browser.

Your password should be protected as confidential. Your use of the password and Intel’s websites are governed by Intel’s Terms and Conditions of Use linked from the bottom of each respective site’s web pages.

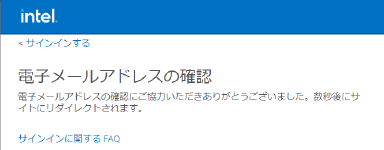

上記は受信したメールの先頭部分です。このlinkをクリックして、アカウント登録を完了させてください。アカウント登録を完了すると、下記のような画面になります。

図6 アカウント登録完了画面

アカウント登録が完了したら、図2の画面からサインインしてください。

●ダウンロード

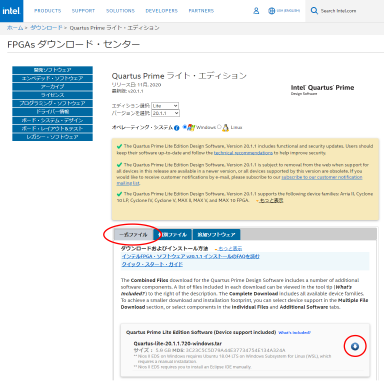

QuartusPrimeライトエディションは、QuartusPrimeライトエディション ダウンロード・ページからダウンロードできます。 初心者はファイル・サイズは多少大きいですが、「一式ファイル」を選択するのが良いでしょう。

図7 QuartusPrimeライトエディション ダウンロード・ページ

ダウンロードしたファイルはtar形式でアーカイブされているので、WinZipなどのツールを使って解凍する必要があります。

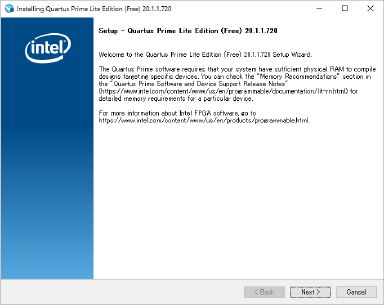

●インストール

ダウンロードしたファイルを解凍したら、その中のsetuup.bat(Windows版)を実行してください。batファイルなのでコマンドプロンプトが表示されます。インストーラの起動まで少し時間がかかります。インストーラが起動すると、次のような画面になります。

図8 QuartusPrimeのインストール開始

以降は基本的に「Next>」を選択していけば問題ありません。途中、ライセンス契約(License Agreement)の確認画面では「I accept the agreement」を選択し、それ以外はデフォルトのまま「Next>」をクリックしていきます。なお、インストール先のHDDの空き容量は20Gバイト程度が必要です。

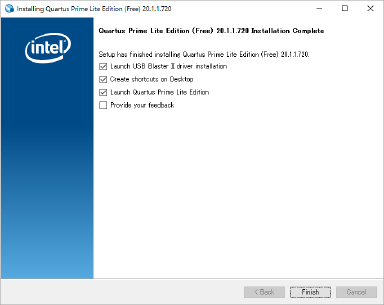

インストールにはしばらく時間がかかります。インストールが完了すると、次のように表示されます。

図9 インストール完了画面

インストール完了後、デバイスドライバのインストールが始まります。これはFPGAダウンロード・ケーブルであるUSBブラスタのドライバのインストール動作です。この時点でFPGA評価ボードを接続していない場合は、インストール途中でエラーが発生しますが、ここでは気にしなくてOKです。

FPGA評価ボードを接続して電源を入れたときに、改めてデバイス・ドライバのインストールが行われます。

●ダウンロード&インスト-ル クイック・スタート・ガイド

ダウンロード&インスト-ル クイック・スタート・ガイドついては、下記PDFにも説明があります。参考にしてください。

ダウンロード&インスト-ル クイック・スタート・ガイドPDF

◆ FPGA開発ツール“QuartusPrime”の使い方

●プロジェクト作成前に…

本特設ページからダウンロードしたファイルを解凍した後に生成される「DE10-Lite」フォルダを任意のディレクトリにコピーしておきます。ここでは例として、D:\FPGA内にコピーするものとします。

●プロジェクトの作成

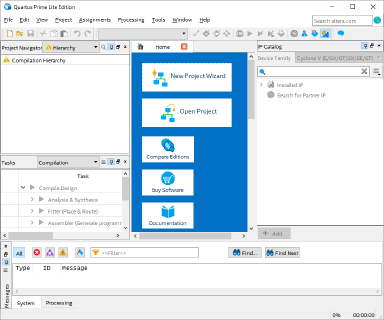

まずはQuartusを起動します。

図10 Quartusの起動ショートカット

Quartusが起動したら、メニュー・バーの「File」→「Nwe Project Wizard」または下記画面の「Nwe Project Wizard」をクリックしてプロジェクトの作成を開始します。

図11 プロジェクト作成開始

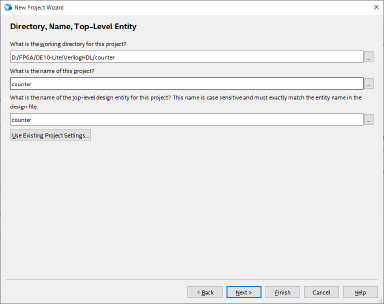

以降は基本的に「Next>」を選択していけば問題ありません。下記の画面でプロジェクトの名前を設定します。ここでは例として、本誌特集サンプル・ソースをコピーしたフォルダ(D:\FPGA\DE10-Lite\VerilogHDL\counter)に、プロジェクトを作成してみることにします。

下図のように、ディレクトリ名を、D:/FPGA/DE10-Lite/VerilogHDL/counter(VHDLを使う場合はD:/FPGA/DE10-Lite/VHDL/counter)に、プロジェクト名をcounterとして、「Next>」をクリックします。

図12 プロジェクト名の設定

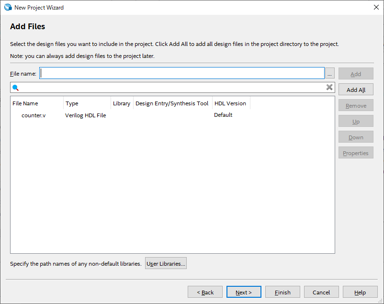

次にHDLソースを読み込みます。「…」をクリックしてファイル選択画面を開き、HDLソースを選択してから「Add」をクリックすると、HDLソースがプロジェクトに取り込まれます。ソースを選択したら「Next>」をクリックします。

図13 HDLソースの読み込み

次の画面ではデバイスを設定します。ファミリ名は「MAX10」、デバイスは「MAX10 DA」、パッケージは「FBGA」、ピン数は「484」、スピードグレードは「7」を選択するとデバイスが絞られるので、右下のスクロールバーを操作し使用するFPGA評価ボードDE10-Liteに搭載されている「10M50DAF484C7G」を選択します。

図14 プロジェク作成のデバイス設定

最後は作成したプロジェクトのサマリが表示されます。「Finish」をクリックしてプロジェクト作成を終了します。

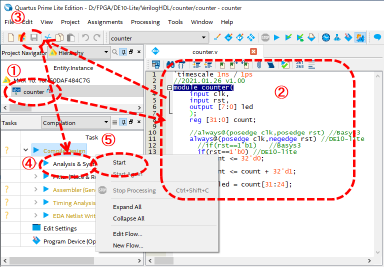

●ソースコード作成とアナライズ

HDLソースをダブルクリックして、エディタで開き内容を編集して保存します。「Compile Design」→「Analysis & Synthesis」→「Start」を選択するとアナライズが実行されます。文法のエラーなどがあれば、ここでエラーが表示されます。

図15 ソースコード作成とアナライズ

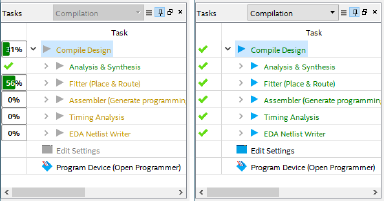

また、アナライズや論理合成など、ツールが時間のかかる処理をしているときは、動作中の処理のプログレス・バーが表示され、完了するとチェックマークのアイコンに変わります。

図16 ツールが処理中/完了時の表示

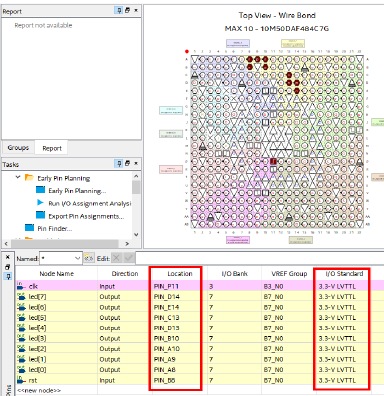

●ピン配置指定

HDLソースの入力が終わったら、メニュー・バー「Assignment」→「Pin Planner」でピン配置ツールが起動するので、信号ごとにピン配置(Location)と信号レベル(I/O Standard)を指定します。

図17 ピン配置指定

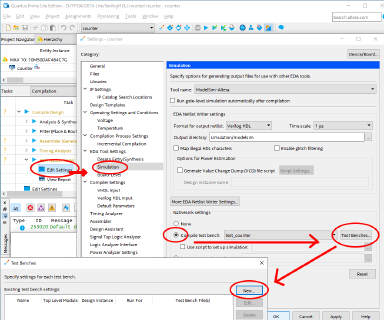

●シミュレーション実行

テストベンチはメニュー・バー「Assignments」→「Setting」または下記の画面のように「Edit Setting」で開いたセッティング画面の中の「EDA Tool Setting」→「Simulation」を選択し、「Compile test Bench」→「Test Benches」→「New」をクリックします。

図18 テストベンチの設定画面

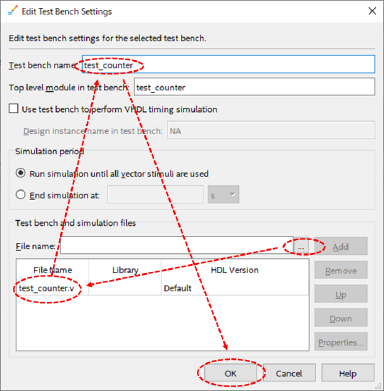

すると下記のような画面が表示されるので、「…」をクリックしてテストベンチ(test_counter.v、VHDLの場合はtest_counter.vhd)を選択・登録し、「Test Becnh name」に「test_counter」を指定して、OKをクリックします。

図19 テストベンチの登録

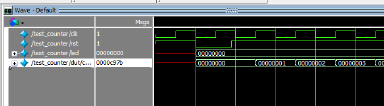

シミュレーションの実行はメニュー・バー「Tools」→「Run Simulation Tool」→「RTL Simulation」を選択します。するとModelSim-Alteraが起動してシミュレーションが実行されます. リセット解除後にクロックが立ち上がると、countがインクリメントされるのがわかります。

図20 シミュレーション波形(ModelSim-Altera)

●論理合成・配置配線・FPGAデータ生成

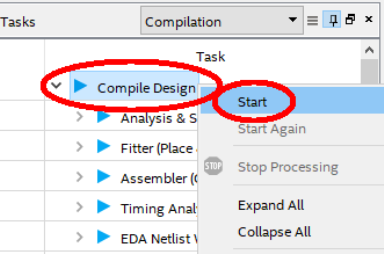

「Compile Design」→「Start」を選択するとAnalysis & Synthesis(論理合成)、Fitter(配置配線)、Assembler(データ生成の実行)が実行される。

図21 論理合成・配置配線・FPGAデータ生成

●FPGAへの書込み

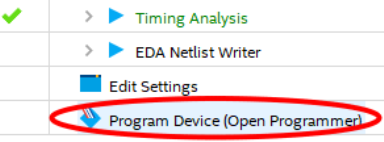

「Program Device」をダブルクリックするとProgrammerが起動します。

図22 Programmerを起動

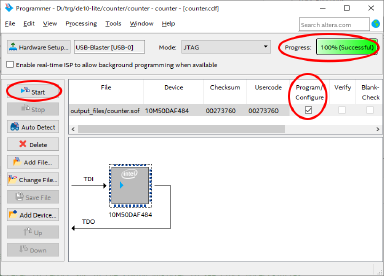

起動後するとJTAGチェーンが検索されてFPGAが検出されます。「Program/Configure」にチェックが入っていることを確認したら、「Start」をクリックすると書き込みが開始されます。右上のプログレス・バーが100%になるとダウンロード完了です。

図23 FPGAへの書込み