# 個別部品で組み立てて動作原理から設計法までを理解する PLL 周波数シンセサイザの設計法徹底解説

第13回 位相比較器のデッド・ゾーンをなくす

アンチバックラッシュ回路のしくみ

小宮 浩 Hiroshi Comiya

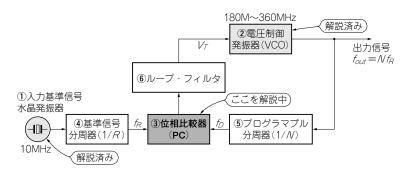

図13-1に,設計/製作しているPLL周波数シンセサイザの基本構成を示します。前々回(第11回,2007年1月号)からは,③位相比較器の解説を行っています。今回は、その最終回となります。

前回(第12回,2007年2月号)は、位相比較だけでなく周波数比較も行える位相周波数比較器PFCの動作原理、そしてそれを3ステート状態にするチャージ・ポンプやOPアンプによる合成回路について解説しました。また、製作する位相周波数比較器の感度特性を実測したところ、位相差0°近くでの感度特性の傾斜がなまっていることを確認しました。

今回は、この傾斜のなまりがPLLにどのように影響するのか、PFCはどうしてこのような感度特性となるのか、これを改善する方法などについて解説します。

## 位相周波数比較器の不感帯 …デッド・ゾーン

位相差に加えて周波数差も検出できる優れたPFCですが、欠点もあります。

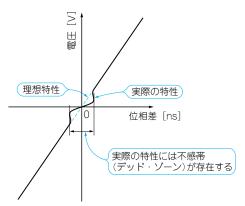

図13-2は、PFCのもつデッド・ゾーン (dead zone;不感帯)のイメージ図を示します。理想的には、図中に記した点線のように微小な位相差も比較検出で

きなければなりません.

しかし、実際には位相差が小さい領域において、図示したようなデッド・ゾーンが存在するのです。そのため、位相差がゼロ近くになると位相比較器の感度 $K_P$ は大幅に低下します。

#### ● デッド・ゾーンが大きいと位相雑音が増える

それでは、デッド・ゾーン(不感帯)の大きな位相比較器を用いると、PLLにどのような影響が及ぶのでしょうか。

デッド・ゾーンの大きい位相比較器でPLLを組むと、ロックして位相差がゼロに近付いた場合、デッド・ゾーンの範囲で動作することになります。その結果、位相比較器の感度  $K_P$ が下がってしまいます。感度  $K_P$ が下がれば、PLLのオープン・ループ・ゲインも低下し、ループ・フィルタ定数によって定めたループのカットオフ周波数は大幅に低くなります。そのため、PLLのフィードバック効果による VCO の位相雑音の抑圧効果が極端に少なくなってしまいます。

デッド・ゾーンが大きいと位相雑音特性の優れた PLLを構成できなくなりますので、デッド・ゾーン はできるだけ小さいことが望まれるのです。デッド・ ゾーンがあることによる悪影響を改善するためには、

図13-1 PLL 周波数シンセサイザの基本構成 前回/前々回に引き続き位相比較器について解説していく

## Keywords

位相雑音, PFC, 位相周波数比較器, アンチバックラッシュ, 比較周波数漏れスプリアス, ADF4110, SA8025, SA7025

図 13-2 PFC のデッド・ゾーン特性のイメージ 理想の特性は原点付近でも直線を保っている

デッド・ゾーンがなぜ生じるのかをまず理解する必要 があります.

#### PFCのデッド・ゾーンは遅れ時間で生じる

PFCにはどうしてデッド・ゾーンが存在するので しょうか. これは、PFCを構成するゲート回路の遅 れ時間 taによって生じます. taの影響で、微小な位相 差を検出できなくなる原因についてB2Spice A/D 2000でシミュレーションして調べてみます.

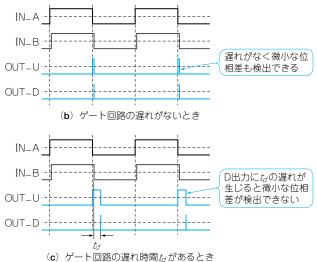

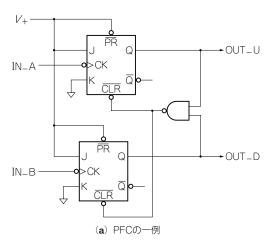

図13-3(a) は、立ち下がりエッジで動作するフリ ップフロップを用いたPFCの一例です. PFCの動作 については、前回(第12回、2007年2月号)で詳しく 解説しましたので、そちらをご覧ください。

#### ▶2入力の位相差がごく少ない場合の動作

この回路で、2入力IN AとIN Bの位相差がごく 少ない場合のシミュレーション結果を図13-3(b) に 示します.

IN\_Aの入力に対してIN\_Bがごくわずか遅れてい ますので、OUT\_Uにその微小な遅れが検出されます. ただし、これはゲート回路の遅れがまったくない理 想素子を用いた場合です.

#### ▶ゲート回路に遅れをもたせた場合の動作

しかし、実際のゲート回路では遅れが生じます.

さまざまな部分に遅れを設けるとわかりづらいので, シミュレーションでは、IN\_Bの立ち下がりで OUT\_Dに一瞬パルスが生じるときに遅れ時間 taをも たせました. すると, 図13-3(c) に示すシミュレー ション結果となります.

$OUT_D$ には、 $t_d$ ぶん遅れた時点で一瞬パルスが生 じ、その時点でOUT\_Uが"L"に落ちることになる ので、位相差パルス長は taぶん長くなり、位相差が 正しく検出できないことになります.

これからわかるように、2入力の位相差が遅れ時間 taに近付くことによって、位相差パルス長の誤差ぶん が大きくなります. さらに、2入力の位相差が $t_d$ よ り小さくなれば、位相差を検出できなくなってしまう のです. これがPFCにデッド・ゾーンが存在する理 由です.

### PFCのデッド・ゾーンを小さくするには高速設計 が必要

デッド・ゾーンが大きいと低位相雑音のPLL周波 数シンセサイザを構成できませんので、デッド・ゾー ンはできるだけ小さくしなければなりません.

そのためには、ゲート回路の遅れ taを減らさなけ ればなりません、すなわち、PFCで位相比較する周 波数がたとえ低くても、PFC 自体は高速設計をする ことになります.

図13-3 PFC にデッド・ゾーンが生じる理由 立ち下がりエッジで動作するフリップフロップを用いた PFC の一例