## 連 載

## 低ノイズ&高効率パワー回路の実験

# 5 フェーズ・シフト PWM 方式 ZVS 可変電源の製作

稲葉 保

今回から、ソフト・スイッチング回路を応用したいろいろな回路を製作していきます。今回は、0 V から 100 V まで出力電圧を可変できるスイッチング電源を製作します。パワー MOSFET を 4 個使用するので、低出力、低コストを目的する用途には不向きですが、数百 W  $\sim$  数kW の高出力用途には、本電源はメリットがあると思います。

ただし私自身,設計手法を確立していない部分があるので、ここではまず回路を製作して、その動作と挙動などを観測しながら、より完成度の高い回路を目指します。製作した回路の異常な環境条件での信頼性、誤動作、ノイズ特性などは保証できませんので、あらかじめご了承ください。

3.3 V/100 A といった低電圧・大電流出力の DC - DC コンバータと異なり、回路技術による効率アップのための工夫が生かせます。

### 0~100 V の出力可変型 スイッチング電源を作る

#### ZVSを採用する

PWM制御が可能で、部品点数があまり増えないといった理由で、フェーズ・シフトと呼ぶPWM制御法を採用することにしました、詳しくは後述します。

パワー・スイッチング回路においては、出力電力が大きい場合、変換効率が悪いと、放熱のための部品追加などでコストがアップしたり、外形が大きくなるといった問題が生じます。特に、スイッチング周波数が高くなると、スイッチング素子の導通損失は同じですが、スイッチング損失は確実に増加します。そこで、スイッチング素子のON/OFF時だけに着目したゼロ・ボルト・スイッチング(ZVS)方式を採用することにしました。

#### ● 仕様

製作した可変電源の仕様を下記に示します.

入力電圧: AC100 V ± 10%

出力電圧: 0~100 V<sub>DC</sub>

出力電流: 0~4 A

- 制御電圧:0~+5 V

- スイッチング周波数:50 kHz

出力電圧が固定ならば、スイッチング周波数をもっと上げることが可能ですが、本回路のように0V付近まで出力電圧を下げる必要がある場合は、このように低くせざるを得ません.

出力電圧が0V付近ではPWM信号のデューティ比が小さくなります。例えば、スイッチング周波数が1MHzだったとすると、PWM制御信号のデューティ比1%のオン時間は10nsしかありません。これではパワー素子の駆動が容易ではなく、直線性が悪くなる可能性があります。

### フェーズ・シフト型 PWM 制御の基礎知識

#### フェーズ・シフト型 PWM 制御の特徴

#### ▶従来のPWM 制御の問題点

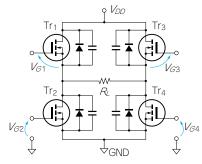

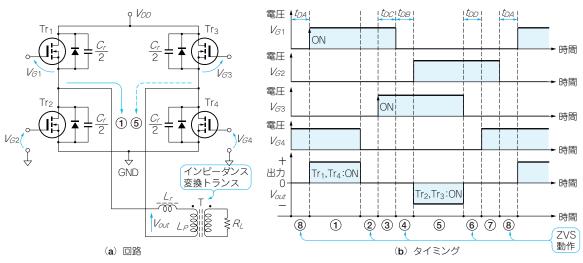

**図5-1** に示すのは、フルブリッジ(Hブリッジとも呼ぶ)回路です。

古典的な PWM 制御では、フルブリッジ回路を構成する 4個のスイッチング素子のうち、 $Tr_1$ と  $Tr_4$ (正出力)、または  $Tr_2$ と  $Tr_3$  (負出力)が同時に ON します。 そして、これらのトランジスタの ON 期間と OFF 期間の比(デューティ比)を変化させて出力電力を制御します。

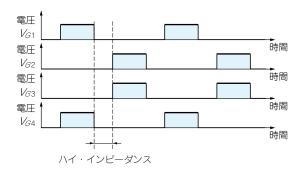

図5-2(a) に制御信号のタイミング・チャートを示します. これを見るとわかるように, 4個のスイッチ

図5-1 フルブリッジ回路

### パワー回路の実験

(a) 一般的なフルブリッジ PWM 動作

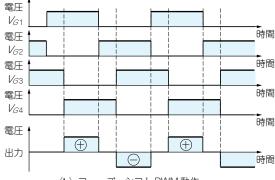

(**b**) フェーズ・シフト PWM 動作

図5-2 古典的な PWM 制御信号とフェーズ・シフト型の PWM 制御信号

ング素子がすべてOFFして、負荷のラインがハイ・インピーダンス状態になる期間があります。負荷がヒータやランプなどのように抵抗性なら問題ありませんが、インダクタンス負荷の場合は、このラインの電位は安定しません。

# ▶フェーズ・シフトのメリットその①…全制御期間において安定したインピーダンスで負荷を駆動できる

図5-2(b)に示すのは、フェーズ・シフト制御したフルブリッジ回路の動作です。各ハーフ・ブリッジ回路は、つねにデューティ比50%で動作し、その位相差だけを変化させてPWM制御を実現しています。このようにすることで、つねにロー・インピーダンス状態で、安定して負荷(スイッチング・トランス)を駆動できます。

# ▶フェーズ・シフトのメリットその②…絶縁ゲート駆動回路をシンプルに構成できる

デューティ比が常に50%なので、パルス・トランスを使うことができます。その結果、シンプルな回路で、パワーMOSFETを絶縁駆動できます。

#### ● フェーズ・シフト制御でZVS動作を実現する方法

図5-3に示すのは、ZVS動作を実現したフルブリッジ回路です。スイッチング素子と並列に共振コンデンサ $C_r$ 、負荷抵抗 $R_L$ と直列に共振インダクタ $L_r$ を挿入します。

ZVS動作の基本は、デッド・タイムを挿入し、この期間にスイッチング素子の電圧の変化率を制限することです。デッド・タイムの時間設定や、 $C_r$ および $L_r$ の定数は、スイッチング周波数、負荷抵抗 $R_L$ 、スイッチング素子の電気的特性などの条件によって決定します。

期間①は $Tr_1$ と $Tr_4$ が同時にON,期間②は $Tr_4$ だけがOFFします。重要なのは期間③です。この期間中は、 $Tr_1$ と $Tr_3$ がONして負荷抵抗が短絡されます。 $Tr_1$ がOFFする期間④で正の半サイクルが終了します。負の半サイクルも同様な動作をします。ZVS動作は期間②、④、⑥、⑧に行われます。

図5-3 ZVS動作を実現するフェーズ・シフト PWM 制御信号

トランジスタ技術 2004年6月号