# 新連載

# 個別部品で組み立てて動作原理から設計法までを理解する PLL 周波数シンセサイザの設計法徹底解説 第1回 最適化設計への準備

小宮 浩 Hiroshi Comiya

# 連載のねらい

● PLL 周波数シンセサイザはいくつかの周波数を切り替えたいときに使う

無線関連の電子回路では、局部発振器として、いく つかの周波数の切り替えが必要です。例えば、テレビ の受信器ではそのチャネルの数だけ発振器が必要となりますが、それをひとつひとつ準備するのは大変です。 このようなときに使われるのが、本連載でとりあげるPLL周波数シンセサイザと呼ばれる回路です。

発振器にはいろいろな形式がありますが、とくに PLL 周波数シンセサイザが使われる理由は何でしょ うか.

193

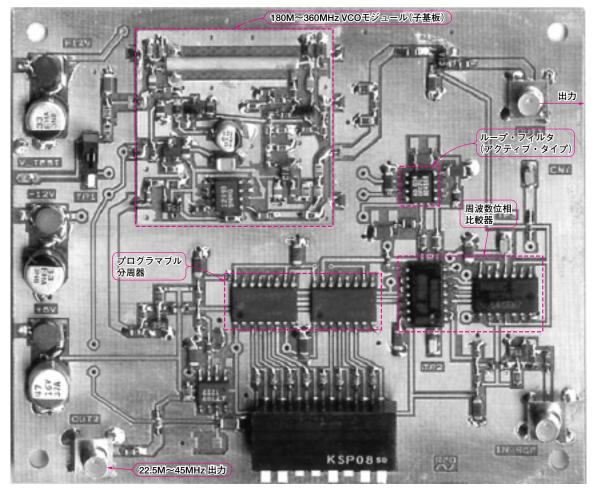

写真1-1 製作する周波数 PLL シンセサイザの外観

**トランジスタ技術** 2006年3月号

### ● 水晶振動子の精度で任意の高周波を作れる

水晶発振器を使えば正確な周波数を作ることができますが、得られる周波数は限定された範囲です.

逆に,高い周波数の発振器を作ることはできても, 正確で安定な周波数を得るのは困難です.

PLL 周波数シンセサイザは、これらのたがいの弱点を補って、水晶振動子の精度を保ったまま、任意の高周波を選択できる自由度をあわせもつ回路です。

### ● 基礎から理解するために個別部品で作ってみる

PLL周波数シンセサイザはたいへん便利な回路ですが、良好な特性を得るためには、基礎的なところから理解している必要があります.

そこで本連載では、回路各部の波形を見ながら実験 学習できるように、集積化されたICを使わず、構成 要素ごとに別々の部品を使います.

ブラック・ボックス化したPLL用ICを用いず、分 周器や位相比較器もすべて安価なディスクリート部品 で構成します。

安価な部品で構成して、広帯域(オクターブ)発振する PLL 周波数シンセサイザの設計に挑戦してみました。 写真 1-1 に、完成した  $180 \, \text{M} \sim 360 \, \text{MHz}$  出力 PLL 周波数シンセサイザの外観を示します。

回路の動作波形を通して、PLLの基本技術を確かめ、自分のものとしてください.

PLL周波数シンセサイザの最高性能を引き出すためのフィルタや発振器の設計法についても、実測データやシミュレータを活用してわかりやすく解説できればと思います。

### ● 注目度が増している技術

携帯電話の普及,パソコン,無線LAN,GPS,デジタルテレビ放送などは,私たちの生活を快適なものとしています.

それらの進展にはPLL(Phase Locked Loop)周波数シンセサイザ技術があったからだ、と言っても決して過言ではありません。

古くは複数のICを組み合わせて作らなければならなかったPLL 周波数シンセサイザですが、今では分周器や位相比較器を一体化したLSIが登場し、超小型化され、数GHzの周波数シンセサイザを部品点数も少なく構成できる時代になっています。

無線システムのさらなる進化とPLLの他分野への応用が加速される中、必要十分な性能とコスト効率を提供するPLL周波数シンセサイザへの取り組みに対する関心も非常に高まっています.

### ● 設計には多様な知識と技術が必要になる

しかしながら、PLL 周波数シンセサイザの設計は

難解です. 特に, 高周波領域でのロー・ノイズ設計になると, さまざまな分野の知識が必要となります.

その分野をおおまかに列挙すると以下になります.

- (1) 高周波発振回路 VCO 技術

- (2) 高周波アンプとミキサ回路技術

- (3) ロー・ノイズ発振回路 VCXO 技術

- (4) 分周回路とロジック・カウンタ技術

- (5) 位相比較回路技術

- (6) フィルタ技術(OPアンプ回路を含む)

- (7) 負帰還回路理論

高周波からロジック,そして負帰還回路理論に至るまでの幅広い知識が必要となります.

現在のLSI化された周波数シンセサイザ用のPLL ICでは、分周器や位相比較器は内蔵されており、直接目に触れることはありません。

しかし、PLLの最適化設計を目指すには、これら PLLを構成する回路技術の基本知識が不可欠となり ます。

# 製作する PLL 周波数シンセサイザの 仕様

### ● 理想的な PLL 周波数を目指して

今回設計し製作する PLL 周波数シンセサイザは教習用ですが、もちろん実用的なものです.

各部の動作波形をチェックでき、また、入手可能な 汎用部品で製作できるように、すべてディスクリート 部品で構成しました.しかし、性能も追求します.

ここで理想的なPLL周波数シンセサイザとはどのようなものか考えてみます.

それは、広帯域発振であり(周波数発振範囲が広く)、 分解能が小さく(周波数設定を細かくでき)、設定スピードも速く、さらに雑音が少なく、そしてスプリアス もないことです。

残念ながら、これらの性能はみなトレード・オフの 関係にあります。すなわち、こちらを立てればあちら は立たずの関係にあります。それがPLLの設計を難 しいものとします。

## ● 採用する部品の制約から周波数を180 M ~ 360 MHz に決める

図1-1に、今回製作するPLL周波数シンセサイザのブロック図を示しました。

この周波数シンセサイザを製作して、その動作解析を行なうことで、PLLの各性能がトレードオフの関係にあることを理解できると思います.

そして,目的に応じた周波数シンセサイザの最適化 設計への糸口を見い出すことができるでしょう.

プログラマブル分周器はCMOSロジックICの74AC163を用いて8ビット・カウンタを組みます。そ