# 特設記事

# ASICを置き換える

ディジタル信号処理デバイス

# 動的再構成デバイス RCF のしくみと スマート・アンテナへの応用

絵野澤 和彦 Kazuhiko Enosawa

本稿では、再構成可能なディジタル信号処理プロセッサRCF(Reconfigurable Compute Fabric)のアーキテクチャについて解説します.

また、その応用事例として、RCF技術を利用した 最初のデバイスであるMRC6011(フリースケール・セ ミコンダクタ)を使ったWCDMAのスマート・アン テナの構築について解説します.

## RCFとは何か

RCF は、大量のデータを並列処理するための再構成可能なディジタル信号処理デバイスです<sup>(注)</sup>.

具体的な用途例として、以前はASICの独占に近い 状態であった移動通信システム、画像処理、マルチメ ディア処理などがあります。

## RCFの基本的な構成要素

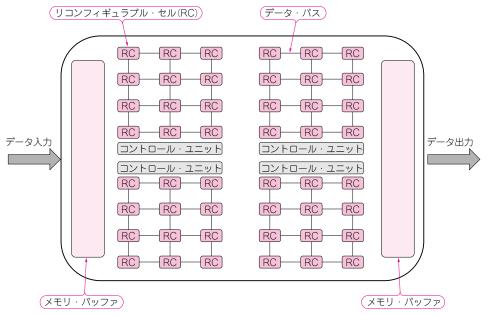

図1にRCFの基本的な構成要素を示します。RCF は以下の四つの要素から構成されています。

- ●算術論理演算を行うリコンフィギュラブル・セル (Reconfigurable Cell: RC)

- RC それぞれをアレイ状に結びつけるデータ・ バス

- 多数並んだRCを制御するコントロール・ユニット

- ●広帯域データをストアするメモリ・バッファ

注:2002年10月,モトローラ半導体事業部(フリースケール・セミコンダクタの前身)は、Morpho Technologies社への株式投資とリコンフィギュラブル技術のライセンス享受を決定した。そのライセンスに基づいてRCFデバイスを開発・出荷している。

189

図1 Reconfigurable Compute Fabric の概念図

データ・バスを含む RC (Reconfigurable Cell) の規則的なアレイとメモリ・バッファ、コントロール・ユニットの組み合わせが RCF の基本的な構成要素となる

**トランジスタ技術** 2005年6月号

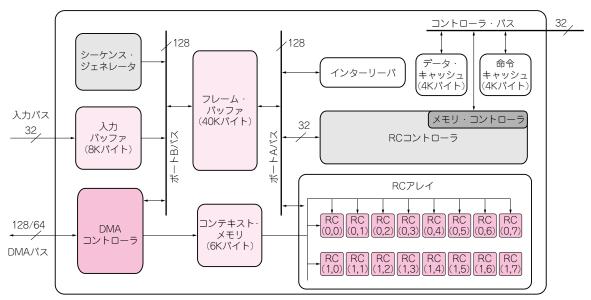

図2 RCFコアのブロック図

32 ビット RISC プロセッサの RC コントローラ、再構成可能な RC アレイ、内部メモリ領域であるフレーム・バッファや RC アレイの命令を記載するコンテキスト・メモリなどを内蔵している。 ブロック・インターリーバとして使える入力バッファ、コンテキストの入力とデータ入出力を行う DMA コントローラを備えている

算術論理演算を行う単位を粒度(granularity)といいます。粒度は、数万ゲート規模のALUや小型のCPUコアのような小規模な演算ユニットからDSPコアやRISCコアのような大規模な演算ユニットまで、一つの演算ユニットの種類や大きさはさまざまです。この粒度の決定は、対象とするアプリケーションに依存します。

#### ● 再構成可能性とは

さて、ここで鍵になるのが、Reconfigurabilityという概念です。Reconfigurabilityは再構成可能性、または再配置可能性と訳されています。以下では、RCF技術における再構成可能性について解説していきますが、ポイントを簡単にまとめると、

### • 並列命令実行

#### ●並列データ転送

を実現する,ということになります.再構成可能性を 実現することで,処理性能に対するチップ面積の削減, 低消費電力化,高演算処理能力が期待できます.

#### RCFが求められている理由

では、なぜ今RCFなのでしょうか. それは、昨今の移動通信システムのように、高速処理が求められる信号処理装置ではソフトウェアという柔軟性を保ちつつ、より早く市場に投入する必要性がさまざまなアプリケーションで求められているからです.

具体的には、信号処理をソフトウェアで行うことに より、ASICの製造のようなハードウェアの設計・検 証サイクルが不要になります。また、プログラムを書き替えることにより、さまざまな規格 [例えば、第3世代移動通信における WCDMA, cdma2000-1x, TD-SCDMA (Time Division-Synchronous Code Division Multiple Access) のような規格 ] や拡張機能 [HSDPA (High Speed Downlink Packet Access) やcdma2000-1x EVDV (Evolution Data and Voice)] に対応することができます。

## RCF のアーキテクチャ

#### RCFコアの概要

図2にRCFコアのブロック図を示します。また、表1にRCFコアの仕様を示します。2行8列の行列状に並べたRCからなる算術論理演算ユニットのアレイ構造をRCアレイといいます。RCは16ビット固定小数点DSPで、この16個の算術論理演算ユニットが並列処理を担当します。

RCアレイの命令はコンテキストと呼ばれ、コンテキスト・メモリに記載されます。このコンテキストは32ビットRISCプロセッサであるRCコントローラにより制御されます。

つまり、RCアレイが演算を行う際、どのような命令パターン(コンテキスト)を実行するかをRCコントローラによりスケジューリングされることになります。

RCコントローラは、4Kバイトの命令キャッシュと4Kバイトのデータ・キャッシュを介してプログラムを実行し、RCFコア全体の制御を行います. 役割