## 計測用16ビットA-D変換の回路技術

多チャネルADCに学ぶ

プロの基板設計ノウハウ

## 第3回 信号源間が共通グラウンド上にあるマルチチャネルADCのループ電流の対策設計

中村 黄三 Kozo Nakamura

前回は、複数のA-Dコンバータを並べたマルチ入力A-D変換基板(以下、マルチチャネルADC)における、信号源間が非導通の場合の基板パターン設計について解説しました。今回は、信号源間が共通グラウンド上にある(非導通ではない)場合のループ電流の対処方法について解説します。

グラウンド・パターンを流れる

ループ電流はノイズの原因

## ● ループ電流の発生要因

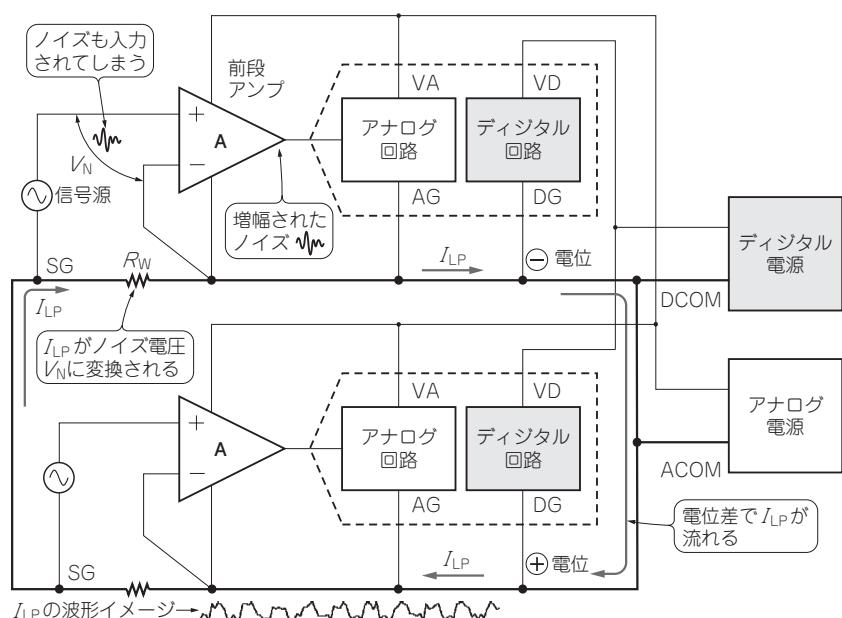

各デバイスで消費された電流は、それぞれのデバイスのグラウンド・ピンから基板のパターンを経由して、アナログおよびデジタル用電源それぞれリターンします(2025年5月号の図2を参照)。このとき、全てのデバイスの瞬時消費電流が時間軸上で一致することはないので、図1で示すように瞬時消費電流の差によるグラウンド間に電位差が生じます。これにより、敏感なシグナル・グラウンド(以下、SG)にダーティなル

ープ電流  $I_{LP}$  が流れるとため、配線抵抗  $R_W$  の両端にノイズ性の電位差  $V_N$  が発生します。

## ● シグナル・グラウンド上に生じる電位差がADCの有効分解能を著しく低下させる

電位差  $V_N$  は、前段アンプにより信号と共に増幅されてA-Dコンバータの入力へ伝達されるので、A-Dコンバータの有効分解能ENOB(Effective Number Of Bit)を著しく低下させます。有効分解能ENOBとは、A-D変換時のS/N比と類似の評価基準です(次号で解説)。

図2はこのような状態におけるA-Dコンバータの出力コードを波形で示したもので、デジタル・コードの値RTO(Refer To Output、出力換算値の意味)をアナログ波形で近似するという意味からデジタルズド波形と呼ばれています。

波高値は前段アンプで100倍に増幅された結果なので、アンプ入力での換算値RTI(Refer To Input)では、配線抵抗  $R_W$  の両端に約12.5mVの電位差  $V_N$  が生じ

図1 マルチチャネルADCの各信号源が共通グラウンドになっている最悪の例

各デバイスの瞬時消費電流の時間差によって上のDGの電位が下のDGの電位より低くなり、敏感なSGにダーティなループ電流  $I_{LP}$  が流れているようす。 $I_{LP}$  がSGの配線抵抗  $R_W$  でノイズ電圧  $V_N$  に変換され前段アンプで増幅されてA-Dコンバータの入力へ伝達される