## 連載

精度不良の70%を占めるADC周辺回路&amp;部品誤差要因を攻略せよ

計測用16ビットA-D変換に学ぶ

プロのアナログ回路設計ノウハウ第6回 時分割チャネル切り替えの速度を左右…

総合セトリング時間の測定テク

中村 黃三 Kozo Nakamura

ADCへの入力チャネル切り替え…

速度を左右する総合セトリング時間を測る

A-Dコンバータ(以降ADC)は1つで、複数の入力チャネルをマルチプレクサ(以降MUX)で時分割切り替えすることができます。特に、各チャネルの測定間隔が高密度であることが望ましい用途に向く処理をオーバラップ・モードと言います。オーバラップ・モードにおけるシステム全体のセトリング時間についての要点は次のとおりです。

- ①各デバイスのセトリング時間の単純加算では求めないので、実験で求めるしかない

- ②知りたいのはアナログ回路の最後段に位置するサンプル&ホールド・アンプ(S/H)の応答遅れ+ $\alpha$ の時間

③システムの総合セトリング時間の中でバッファ・アンプに使うOPアンプのセトリング時間が一番長く支配的

出荷前にたくさんのバッテリの端子電圧を高速にスキャンするなどの用途に向きます。

今回は、総合セトリング時間を観測する方法であるエッジ・シフト法と、エッジ・シフト法による測定用治具の測定原理と回路を解説し、①～③の実測結果を考察します。

課題…オシロスコープで

総合セトリング時間は直接観測できない

## ● オシロスコープによるセトリング時間測定の問題

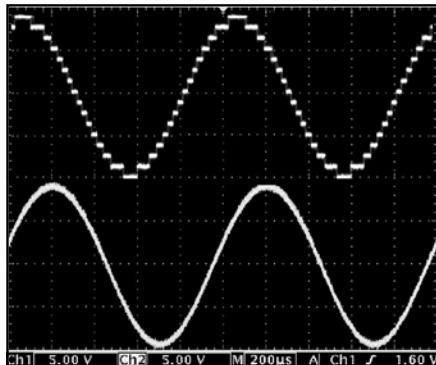

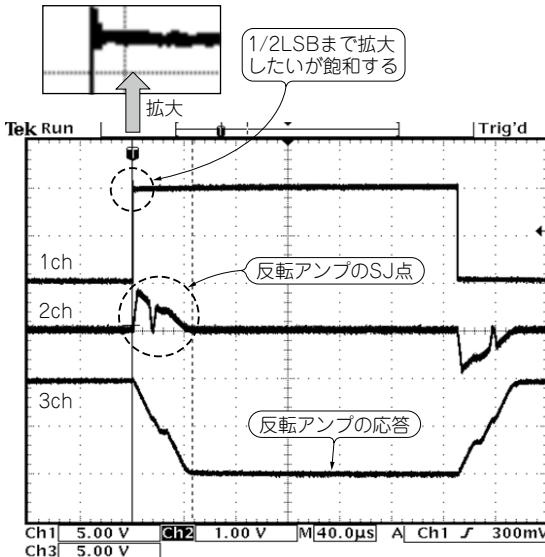

図1(a)はオシロスコープによるOPアンプのステップ応答波形(1chの掃引)です。オシロスコープによる観測は簡便ですが、立ち上がりエッジのリンクギング・テールが1/2 LSB(16ビット0～5V入力のADCでは電圧換算で76.3 μV)まで収束する時間を測定するのは

- (a) オシロスコープで観測したバッファのステップ応答波形…

セトリング時間の測定は困難(1ch : 5V/div, 2ch : 1V/div,

3ch : 5V/div, 40μs/div)

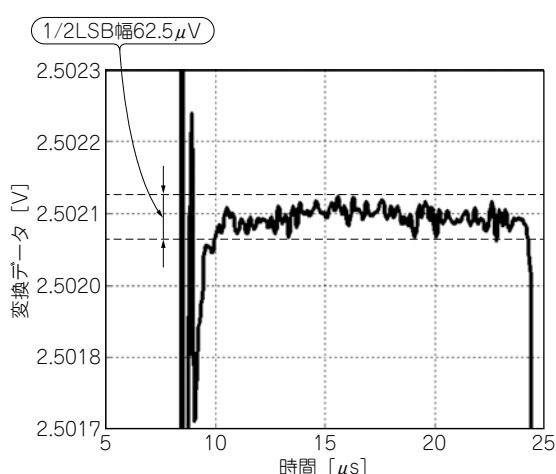

- (b) エッジ・シフト法でADCを動作してExcelで作図した波形…

セトリング時間を特定できる

図1 セトリング時間はオシロスコープでの測定が困難…エッジ・シフト方式がおすすめ

反転アンプ構成ならオシロスコープでサミング・ジャンクションの電圧収束時間を測りセトリング時間を割り出すことは可能