## 連載

| 0C | X1648    | 00        | 00        |

|----|----------|-----------|-----------|

| 10 | MM_M48s  | -----00   | -----00   |

| 14 | MM_M48s  | M0TtCPU   | -----00   |

| 18 | CC32     | -----00   | CC32 2    |

| 20 | CLK      | -----00   | RSIn(ILS  |

| 22 | 00000000 | 000000011 | 000000011 |

| 24 | KP_LINE  | 10        | KPcolumn  |

| 26 | 00001111 | 00111111  | 00111111  |

| 28 | MEM      | 00        | 21        |

| 30 | -----00  | MEM       | 01        |

| 32 | -----00  | -----00   | -----00   |

Verilog HDLによるロジック回路設計＆実機デバッグの実際

# FPGA内部信号が丸見え！ モニタ表示回路の製作

## 第8回 小型FPGAボードCmod A7-35T 実機テスト回路の全体像

木村 真也 Shinya Kimura

本連載で紹介しているFPGAの内部信号を外部モニタに表示する回路(FPGA内部信号VGA表示IP)の動作を試すために、FPGA内でテスト回路を動かしてみます。

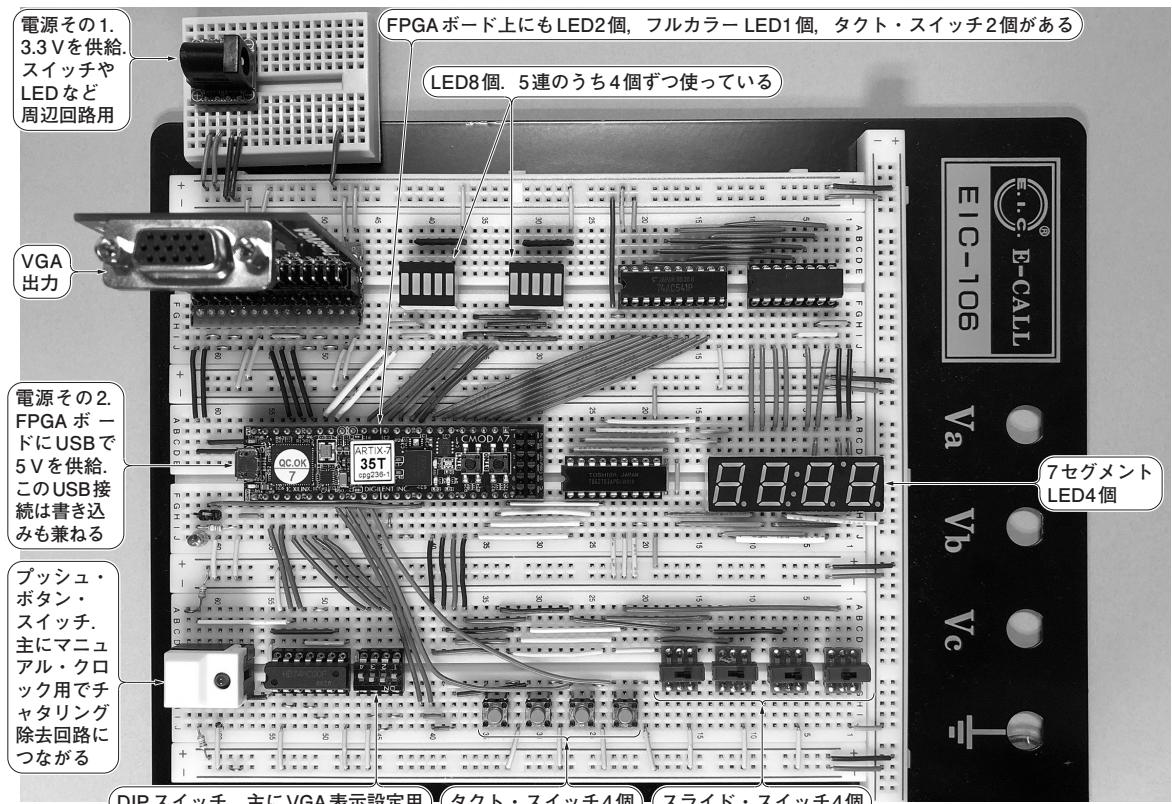

そのテスト回路のクロックや入出力として、写真1のような周辺回路と、周辺回路とテスト回路を接続するためのHDLや設定ファイルを準備します。

### 実験回路のベース… FPGAボード&VGA回路

#### ● 使用するFPGAボードCmod A7-35T

本連載向けには、FPGAとしてArtix-7(AMD社)ファミリのXC7A35Y-1CPG236Cを搭載しているCmod A7-35T(Digilent)を選びました。48ピンDIP形状(約18 mm × 70 mm)の小型ボードで(写真2)、ブレッドボードへ装着して使えます。

電源は、ホスト・パソコンとUSBケーブル(Micro

写真1 「FPGA内部信号VGA表示IP」の動作実験回路の全体像…FPGAボードとVGA出力以外にも便利なスイッチ表示器を用意しておく

第1回 製作するFPGA内部信号まる見え回路IPの特徴 (2025年7月号)

第2回 VGAモニタへのFPGA内部信号の表示の詳細 (2025年8月号)

第3回 FPGA内部信号丸見えIPの具体的な回路構成 (2025年9月号)