## テクノロジ・トレンド Technology Trend

100 個からの少量生産向きゲート・アレイが登場

# ゲート・アレイ最新事情

FPGAの普及により、ロジック回路設計はより手軽で身近なものになりました。その一方でゲート・アレイも多数使用され続けており、ゲート・アレイの技術も着実に進歩しています。また、100個~の少量発注が可能な製品が登場し、ゲート・アレイの選択肢も広くなっています。ここでは、ゲート・アレイの最新事情を解説します。〈編集部〉

近藤 利行 Toshiyuki Kondo 橋本 晋 Susumu Hashimoto 加藤 毅紘 Takehiro Katou

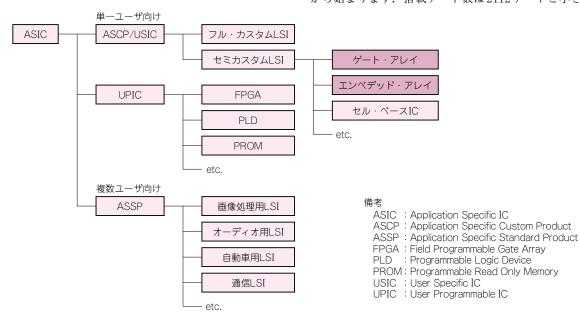

製品サイクルの短期化が進むなか、開発者は製品開発期間の短縮とともに機能の差別化が求められています。そして、他社との差別化を図った製品をいちはやく市場に投入するために ASIC (Application Specific Integrated Circuit:特定用途向け集積回路)が盛んに使用されています。 ASIC はその構造や用途により、図1に示すようにセル・ベースIC、ゲート・アレイ、FPGA などのいくつかのカテゴリに分類されます。

開発者はコスト,開発期間,性能の三つの観点から 開発する製品にもっとも適したデバイスを選択し,開 発競争を勝ち抜かなければなりません.本稿では古く から通信機器,産業機器,民生機器などさまざまな分 野で利用されているゲート・アレイについてその概要, 最新技術および使用例について解説します.

### ゲート・アレイとは?

#### ● ゲート・アレイの歴史

ゲート・アレイの歴史は古く、初期のゲート・アレイはTTLやECLなどのバイポーラ・トランジスタによる構成が採用されていました。TTLはやがてBiCMOSへと移行し、高速動作が要求される場合に使用されてきましたが、CMOSプロセスの微細化による高集積化、高速化および低電力化のため、現在のゲート・アレイはCMOSへと集約されています。本稿ではNECエレクトロニクスのCMOSゲート・アレイを例に説明します。

CMOS ゲート・アレイの歴史を**表1** に示します。 CMOS ゲート・アレイは 1982 年に  $3.0~\mu$ m プロセス・ノードを採用した CMOS -2 シリーズを開発したことから始まります。 搭載ゲート数は 2112 ゲートと小さ

図1 ASIC の分類

ASIC は、セル・ベース IC、ゲート・アレイ、FPGA などに分類される

| 西暦   | 1982     | 1983        | 1984       | 1987     | 1990     | 1992     | 1997                | 1998               | 2001                 | 2005            |

|------|----------|-------------|------------|----------|----------|----------|---------------------|--------------------|----------------------|-----------------|

| プロセス | 3.0 μ m  | $2.0~\mu$ m | $1.6\mu$ m | 1.2 μ m  | 1.0 μ m  | 0.6 μ m  | $0.35\mu\mathrm{m}$ | $0.5\mu\mathrm{m}$ | $0.25  \mu  {\rm m}$ | 0.15 μ m        |

| シリーズ | CMOS - 2 | CMOS - 3    | CMOS - 4   | CMOS - 5 | CMOS - 6 | CMOS - 8 | CMOS - 9HD          | CMOS - N5          | CMOS - 10HD          | CMOS - 12M      |

| ゲート数 | 2 K      | 11 K        | 19 K       | 24K      | 177 K    | 627K     | 2500K               | 123 K              | 2600 K               | 4100 K/2.7 Mビット |

| 動作電圧 | 5 V      | 5 V         | 5 V        | 5 V      | 5 V      | 5 V      | 3.3 V               | 5 V/3.3 V          | 2.5 V/1.8 V          | 1.5 V           |

| 配線層数 | 2        | 2           | 2          | 2        | 3        | 3        | 4                   | 2                  | 4                    | 6               |

表1 ゲート・アレイの歴史(NECエレクトロニクスの例)

く、構造は配線領域とセル領域が分離されたチャネル 構造でした。設計手法としてはCADによる設計手法 はほとんど普及していないため、人手により回路図作 成からレイアウト図作成までが行われ、マスク設計完 了後のディジタイズ処理にCADが使用される程度で した。

半導体プロセスの進化とともに半導体の集積度が向上し、ASICの開発数が急激に増加し始めたのが1990年代前半です。1990年には1.0 μmプロセス・ノードのCMOS-6シリーズが開発されました。CMOS-6シリーズでは配線領域とセル領域が一体となったチャネルレス構造が採用されるようになりました。チャネル構造とチャネルレス構造の違いを図2に示します。

チャネル構造では、ブロック間の接続に使用される配線専用の領域とブロックを配置できる領域が別々に用意されています。配線層数が2層のゲート・アレイでは、ブロックを構成するために $1\sim2$ 層が使用されるため、ブロック間の配線を行うためには、配線専用の領域が必要でした。

ただ,配線領域とセル領域が交互に配置されるため, 大規模なメモリなどは配置することができず,また, 回路規模が大きくなると配線領域の使用効率を上げる ことが難しく,結果的にチップの集積度は上がりにく くなります.

(a) チャネル構造

大規模なシステムの1チップ化を可能にする.配線領域の幅やゲートの形を自由に決めることができ,メモリを効率良く搭載することもできる

(b) チャネルレス構造

#### 図2 チャネル構造とチャネルレス構造

一般的に現在のゲート・アレイではチャネルレス構造が使用されている

一方、チャネルレス構造では、配線専用の領域は用意されておらず、チップ全面がブロックを配置可能な領域となります。配線はブロックが配置されていない領域や、ブロックの上層が使用されます。メモリなどの大規模ブロックも配置でき、集積度も上がりやすくなります。そのため、以後のゲート・アレイではチャネルレス構造が一般的に使用されるようになりました。

1992年には $0.6 \mu m$ プロセス・ノードの CMOS-8シリーズが開発されました。CMOS-8シリーズではプロセス・ノードはサブミクロンの時代に突入し,搭載ゲート数は最大627 Kゲートに達しました。CMOS-6、CMOS-8シリーズの開発件数は増加の一途をたどり、1990年代前半から中盤はゲート・アレイ全盛期と言えるでしょう。

一方で1990年の中盤からはセル・ベースICの実用化が始まり、大規模な製品で使用されるようになっていきました。また1990年代の後半から2000年代の前半にはFPGAの出現によりゲート・アレイの開発件数は徐々に減少し、ゲート・アレイは転換期を迎えたと言えます。

ゲート・アレイの製品展開としては、その後も0.5  $\mu$ mプロセス・ノードのCMOS-N5シリーズ、0.35  $\mu$ mプロセス・ノードのCMOS-9HDシリーズ、0.25  $\mu$ mプロセス・ノードのCMOS-10HDシリーズ、0.15  $\mu$ mプロセス・ノードのCMOS-12Mシリーズが開発され、現在も使用されています。なお、CMOS-12Mシリーズに関しては後述します。

#### ゲート・アレイの構造

ゲート・アレイの内部構造を図3に示します。ここでは主流であるチャネルレス構造を示します。チップ内部の構造は、内部セル領域、入出力バッファ領域および入出力パッド領域の大きく三つの部分に分けられます。

内部セル領域は、2入力NANDゲートを構成できるNchトランジスタ2個、Pchトランジスタ2個で構成された基本セルを内部セル領域全面に敷き詰めた構造となります。ゲート・アレイ・ベンダ(ゲート・アレイを提供する企業、NECエレクトロニクス、富士通、エプソンなど)は、この基本セルを複数使用してNANDゲートやNORゲートなどの組み合わせ回路、