### 特集\*トランジスタで学ぶディジタル回路

### 第5章 同期式回路設計の基本を カウンタを作りながら学ぶ

## 基礎からの順序回路設計

井倉 将実

ディジタル回路設計に携わるうえで,避けては通れない回路設計の大前提の概念に「同期」,「非同期」という言葉があります.

同期,非同期は、どれほど高速で優秀なプロセッサやビデオ・チップの設計でも、逆に風力計や地震計,また身近にある時計のように非常に低速なディジタル回路設計でも、必ず考慮しなければならないキーワードです。

### 同期回路と非同期回路の概念

# ● 同期回路とは…クロックの変化に合わせて回路全体が動作するディジタル回路

同期/非同期とは、動作の基本となる何らかの脈動 に応じて動くのか、それとも手前勝手で動作するのか の違いです。

脈動とは、ディジタル回路の世界では「クロック (clock)」と呼ばれ、そのクロックに同期して回路全体が動作すればそれは同期回路です。逆に、クロックの動きとは関係なく動作すれば、それは非同期回路となります。

### ● ディジタル時計の例で同期/非同期を考える

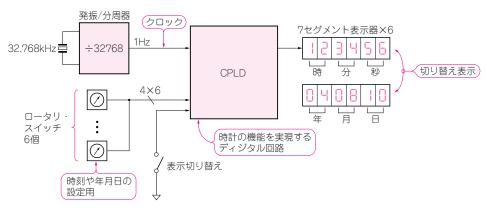

図5-1のブロック図に示すような,時計用ICとクロックを作り出すオシレータ(発振器),表示用の液晶パネルと日時と時間を切り替えるスイッチが乗っているディジタル時計の例をとって,同期/非同期について考えてみましょう.

オシレータは、正確に1秒ごとの時間を刻むクロックを出力します。時計用ICは内部に年、月、日、時、分、秒という数を数える機構をもっています。表示装置は年月日、また時分秒をスイッチ入力に応じて切り替えできます。

この時計には同期回路と非同期回路が入り込んでいます.

#### ▶秒を数える

まず、時計用ICは1秒ごとに1回だけ送られてくる クロックに同期して、秒を数える回路を駆動します。 1秒間に1回ずつ、秒のデータを加算していくという わけです。

その結果、59回数えて次の1回でゼロに戻るか(同期リセットという)、60回数えた瞬間にゼロに戻るか(非同期リセットという)で、秒を数える回路が完成します。

図5-1 ディジタル回路による時計のブロック構成

**トランジスタ技術** 2004年9月号 153

### ▶分を数える

分を数えるにも同様に、秒の結果が「59秒」になった次のクロックで、分の位を加算する方法(同期式)、秒の結果が「60秒」になった瞬間を検出して分の位を加算する方法(非同期式)の二つの方法があります。

また、分という位は $00\sim59$ までの60値しか存在しませんから、秒の位の回路と同様に、「59分」の後には「00分」に戻るリセット処理にも、同期回路/非同期回路の二つの方法があります.

\*

このように、時であれば分の結果を60回数えて加算したりゼロに戻ったり、日であれば時の結果を24回数えて加算したりゼロに戻ったりと、年月日なども同様な動作をします。

4年に1回のうるう年による補正も、その年がうる う年であるかどうかで、日の結果を1日多く追加する というわけです。

#### 非同期式時計ではありえないことが起きる!?

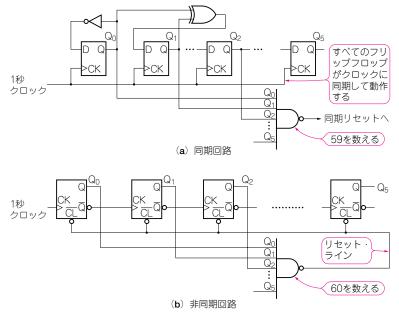

図5-2は同期式と非同期式で、秒/分の管理回路を表したものです。同図(a)が同期式、同図(b)が非同期式で組み上げた回路です。どちらの回路でも、人間の目から見れば見かけ上の結果はまったく同じ値を出力します。

数を数えるタイミングが1秒などという,最新のディジタル回路から比べれば途方もなく遅い時計程度の回路であれば,どちらの回路でもよいと私は思っています.しかしながら,ちょっと高速な回路設計を行うようになると,われわれ回路設計のプロから見れば

「誤動作が含まれる非同期式回路は敬遠したい」ということになります.

細かい理由は後述しますが、図5-3に秒回路を同期式と非同期式で構築した場合に、数を数えて「00秒」に戻る部分の時間的動作を示してあります。

(a)は「59秒」を数えてから「00秒」に戻るときの「リセット条件」の信号が、クロック・パルス幅と同一の1秒間だけ出力されます。

これに対して(**b**)では、「00秒」に戻るときの「リセット条件」が、非常に短いパルスでしか出てきません。このパルスの動きを厳密に見ると、

- ① AND ゲートが秒回路の結果が60であることを認識する

- 2 秒回路のリセット・ラインにパルスを出力する

- ③ AND ゲートが秒回路の結果を60以外(00になっているから)であることを認識する

- ④ 秒回路へのリセット信号出力が抑制される という動作の結果が、リセット・パルス幅の長さにな ります.

この動作を図5-3(b)で細かく見てみると、非同期 回路の場合には瞬間的に「60秒」という、ありえな い数字を数えているのです。

もうちょっと頭をひねって、意地悪に考えてみることにしましょう.

図5-2(b)の回路が図5-3(b)のように動作する非同期回路で、ANDゲートの動作が入力から出力が出るまでに仮に0.5秒かかるとしてみましょう。つまり、ANDゲートの遅延時間 $t_{PD}$ を0.5 s とした場合です。

秒の結果は「58秒」、「59秒」ときて、なんとここ

図5-2 分/秒を数える回路を同期式と非同期式で比較する