### ディジタル・ロジック回路超入門 重点企画

第3章

# 順序回路の機能イメージと その応用

です.

同期回路を加えたラッチ

ムを制御、監視するための信号です。

3(a) のような回路の動作を考えてみましょう.

三原 順-Junichi Mihara

ることは、図1(b)のORにインバータを追加し、AND

の入力側にもインバータを追加すれば明らかでしょう。 このようにRSラッチではRとSがLのときは出力

状態は変化しません. また. RとSがHのときは. 図

2(a)ではQと-QともLになりますが、別の構成の RSラッチでは、そうならないものもあります、一般

にRSラッチではRとSともにHのときの出力は不定

ディジタル同路ではよくクロックという言葉が使わ

まず、RSラッチの前段にANDゲートを付加した図

AND ゲートの動作で述べたように、AND ゲートの

一方の入力は制御信号と考えることができます. した

がって図3(a)のCは制御信号で、CがHのときのみ、

RSラッチはS<sub>1</sub>入力、R<sub>1</sub>入力にしたがって動作します。 では、制御信号Cに幅の広いパルスを用いた場合と、

幅の狭いパルスを用いた場合の違いを考えてみましょ

れます. この信号は一般には各種論理回路がこの信号 によって. いっせいに(同じ時刻に)働くようにシステ

## ● ラッチ(フリップフロップ)の基本動作

ば、出力はその組み合わせによって一意的に決まりま した. このような回路を組み合わせ回路と呼んでいま

が現在の入力と過去の入力に依存する回路を順序回路 と呼んでいます。順序同路においてもっともよく用い られるのがラッチ(フリップフロップと呼ばれること も多い、本稿では以下、ラッチと呼ぶ)です。

ラッチは二つの安定状態をもつ素子です。 例えば、 図1(a)はSがいったんHになると、出力QはつねにH になる同路です。この同路ではQをLにすることはで きませんから、一つの安定状態が**H**しかありません、

これに対して図1(b)では、フィードバック信号Q をRによって制御しているため、二つの安定状態が存 在します、すなわちRがLのとき、SがHになるとQ はHになり、その状態が保持されます、そしてSがL のときRがHになると、出力QはLになり、その状態 を保持します(図1(c)).

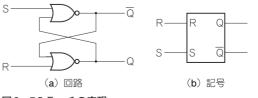

この回路はRSラッチと呼ばれ、一般に図2のよう に表現されます。図1(b)と図2(a)の同路が等価であ

> (a) Sがいった S んアクティ ブになると (b) 二つの安 定状態が ある SET信号 (c) タイム RESE 信号 二つの安定状態

CがHのときのみ $R_1$ と $S_1$ が有効ですから、Cの幅 が広いとCがHのときに $R_1$ と $S_1$ がHになったり、 $R_1$

$\& S_1 \vec{N} + O \& S_2 \vec{N} + O \& S_3 \vec{N} + O \& S_4 \vec{N} + O \& S_$ 出力Qoが変化するタイミングを定めることはできま せん.

一方、Cのパルス幅が狭いと出力QoはCがHにな ったときに変化する可能性が多くなります. つまり. パルス幅の狭い信号Cを用いれば出力Qoの変化のタ イミングを、信号Cの入力タイミングに合わせること ができるわけです(図3(b)).

このように動作のタイミングを制御信号によって設

図2 RSラッチの表現

## 順序回路の登場

第2章で述べた回路では、入力信号の状態が決まれ

これに対し、回路内に記憶素子を含み、求める出力

図1 ラッチの

基本回路