# 第2部 実践編

### **第5章** 1 μV の微小信号や GHz 超の RF/ディジタル信号を正しく伝える

(性能アップ - 技 10

## アナログ・センスで基板を描く③ ノイズ対策

山田 一夫 Kazuo Yamada

実際の基板には目に見えない寄生インダクタンスや寄生容量が存在します. 基板設計が悪いと, 寄生インダクタンスが大きくなりノイズを発生させます. ノイズを対策するには, どの配線を変更し, どのような経路で電流を流せばよいのかを知る必要があります.

本稿では3次元イラストやシンプルな*RLC*回路を用いて、ノイズの原因と対策を解説します。本テクニックは、10 Gbps を超える USB3.2 や SDIインターフェースの高速ディジタル基板、900 MHz 以上のWi-Fiモジュール搭載のRF基板の設計の基本にもなります。 〈編集部〉

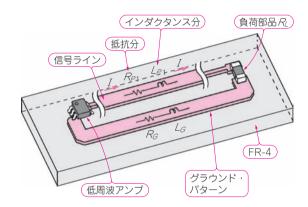

#### 要点① ループは小さくする

図1に示すのは100 Hz~数百 kHz の信号が伝わる 単線のプリント・パターンです。低周波IC の信号出 力から負荷まで1本のプリント・パターンでつながっ ています。このようなプリント・パターンでは、図1 (a) に示すように、IC →信号パターン→グラウンド・ パターンを経由して、アンプのグラウンド端子まで低 周波のリターン電流Iが流れます。

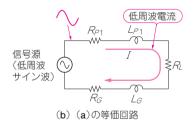

図1(b)に図1(a)の等価回路を示します。図1に示したような片面基板では、全体のループ・インダクタンスと配線抵抗によって、負荷に発生する電圧が決まります。

各配線のインダクタンス成分は、信号パターンとグラウンド・パターンだけでは決まりません。行きと帰りのプリント・パターンで形成されたループの大きさが異なると、全体の配線インダクタンスも変化します。そのため、ループ面積が大きいと配線インダクタンスも大きくなります。

さらに周波数の上昇にともない配線インダクタンス 分で発生する電圧も大きくなり、負荷で得られる電圧 が異なります.

出力電圧の誤差を減らすには、グラウンド・パターンを信号パターンに沿わせるように描きます. これによりループ面積が減り、配線インダクタンスが下がります. ただし行きと帰りの電流が同じ大きさになるよ

(a) 片面基板の配線パターン例

図1 配線パターンのループ面積を小さくするとノイズが低減する

うに配線を設計します.

#### 要点② 繊細なアナログ信号の配線を ディジタル信号の配線で挟まない

100 MHz以上の信号の伝わり方は**図1**で示した伝わり方と異なります.

図2(a)に示すプリント・パターンでは、信号線とグラウンド・パターンが近くに平行に配線されています。片面基板上にはディジタルICが配置されています。

図2(b)に図2(a)の等価回路を示します。 $IC_1$ から信号線にディジタル信号が送り出されます。低周波信号とは異なり、ディジタル信号はほぼ光の速さで、平行

【セ**ミナ案内**】[実習セミナ] [演習あり] 実習・ARMコア内蔵FPGAのハードウェア開発入門~ Xilinx社 Zyng 編

——Lチカから高位合成による本格IPまで

112

【講師】小林 優 氏, 7/25(木)~26(金) 36,000円(税込み) https://seminar.cqpub.co.jp/