# 第5章

# FPGAのロジック回路設計

USBマイコンからデータを取り出して I<sup>2</sup>S フォーマットに並び替える

田力 基 Motoi Tariki(ElecrtArt)

本章では、FPGA内部の各機能ブロックごとに、 その動作の詳細を説明します。FPGAは、USBマイコン内部のメモリ(FIFO)に蓄えられたオーディ オ・データを取り出し、並べ替えます。並べ替えが 完了したら、3線式のオーディオ・インターフェー スを介してD-Aコンバータに出力します。

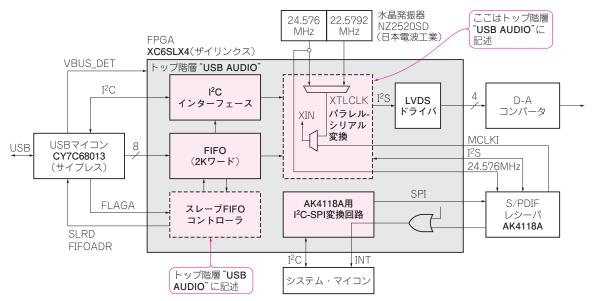

図1 USB-FPGA基板に搭載したFPGA(XC6SLX4)の内部構成

## 回路ブロックの全体像

図1に示すのは、USB-FPGA 基板上のFPGA XC6SLX4(ザイリンクス)の内部構成です。

#### ● 回路ブロックその1:I<sup>2</sup>Cインターフェース

USBマイコンCY7C68013(以下FX2LP)との $I^2$ C通信用のブロックで、 $I^2$ Cのスレーブ・デバイスです。内部の1バイト・レジスタの下位3ビットにFX2LPからサンプリング周波数が書き込まれます(Writeされる). USBマイコン(FX2LP)からの読み出し(Read)要求

に応えて、2 K ワード FIFO 内部(後述)のデータ・バイト数の上位8ビットを送信します。このブロックの VHDL ソース・コード中の回路モジュール名(エンティティ)は "I2CIF" です。

### ● 回路ブロックその2:2KワードFIFO

USBマイコン(FX2LP)からスレーブFIFOモード経由で受信した8ビット・オーディオ・データを、USB-FPGA基板上のオーディオ・クロックに同期して取り出すためのタイミング調整用FIFOです。このブロックのVHDLソース・コード中のエンティティ名は"fifo\_generator\_v8\_2"です。