## 連載

精度不良の70%を占めるADC周辺回路&部品誤差要因を攻略せよ

## 計測用16ビットA-D変換に学ぶ プロのアナログ回路設計ノウハウ

### 第5回 マルチプレクサを使った 時分割A-D変換の設計ノウハウ

中村 黃三 Kozo Nakamura

今回は、アナログ・マルチプレクサ(以後、MUX)で複数の信号を切り替えながら1個のA-Dコンバータ(以後ADC)により時分割処理を行うときのセトリング時間の考え方を解説します。

#### 複数入力チャネルでADCは1つ… 時分割A-D変換の要点

##### ● 時分割処理のキモはセトリング時間

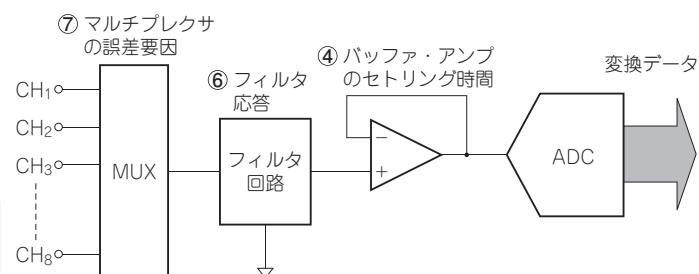

図1は、MUXにより複数のアナログ信号を1つのADCで数値化する場合の要点を示しています。ADCのスペック以外は、④バッファ・アンプのセトリング時間、前置フィルタの⑥フィルタ応答、⑦MUXのメモリ効果による誤差要因です。

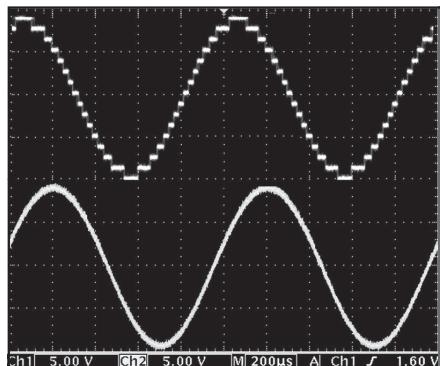

DCレベルが大きく異なるチャネル間の切り替えではMUXの出力はステップ波形となります。そこで、同図のように前置フィルタがMUXとバッファの間にに入る構成では、前置フィルタには周波数特性の切替えても時間波形のリング・テールが長くなるチェビシェフ応答のフィルタは避けるべきです(各フィルタ応答の波形は第4回図7参照)。

④のバッファ・アンプのセトリング時間は、後述するオーバラップ・モードでチャネルあたりのスキャン速度を最大化する場合に重要となります。加えて、MUXからADCのサンプル&ホールド回路(以後、S/H回路)までの総合セトリング時間も定量的に把握する必要があります。

##### ● 時分割処理にはシーケンシャル・モードとオーバラップ・モードがある

MUXの切り替えタイミングを図2に示します。(a)シーケンシャル(またはワンショット)モードと(b)オーバラップ・モードとがあり、図2はチャネル切り替えにおけるそれぞれの変換プロセスを示したものです。

図中の時間分類 $t_{ACQ}$ や $t_{STL}$ は、本稿での説明に用いたもので一般性はありません。デバイス・メーカーのデータシートも各社で統一は取れておらず、読み手から見た場合、不便極まりないところです。

#### 時分割A-D変換①… シーケンシャル・モードの回路構成

##### ● 用途

シーケンシャル・モード方式に向くのは、計算による2次物理量などA-D変換データの後処理に主体を置き、変換間隔が不定期でもよいアプリケーションです。チャネルを切り替えてA-D変換し、そのデータの後処理が終わったら別のチャネルに切り替えてまたA-D変換というように、回路動作が順を追って行われることからシーケンシャル・モードと呼ばれています。

##### ● 適した前置フィルタ

アプリ例は、図3(a)で示すように各チャネル切り替えまで時間的に余裕があり、かつチャネルあたりのA-D変換間隔が不均一で高密度でない運用のものです。こうしたアプリでは、図1のようにMUXとバッファの間にバターワース応答かベッセル応答の前置フ

図1 マルチプレクサにより複数のアナログ信号を1つのADCで数値化する場合の要点

ADCのスペック以外に、④バッファ・アンプのセトリング時間、前置フィルタの⑥フィルタ応答、⑦MUXの誤差要因について配慮が必要。第1回、図2より抜粋