## 連載

Verilog HDLによるロジック回路設計&実機デバッグの実際

# FPGA内部信号が丸見え! モニタ表示回路の製作

第6回 FPGAの機能 IP…フォント等のデータ ROM & 25.175 MHz クロック回路の生成

木村 真也 Shinya Kimura

#### ● FPGAの中に作るディジタル回路を観測したい

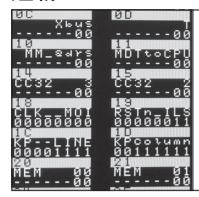

FPGAはいろいろなディジタル回路が作り込めますが、その動作をロジック・アナライザやオシロスコープのような測定器で観察するには、FPGAの外部に信号を引き出す必要があります。FPGAメーカが提供するロジック・アナライザIPもありますが、もっと直接的かつリアルタイムにモニタへ値を表示するために、本連載では内部信号を外部モニタへ表示する回路(FPGA内部信号表示IP)を紹介しています(図1).

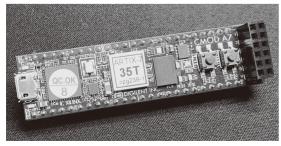

ターゲットに**写真1**に示すCmod A7-35T(Digilent) というFPGA基板を使います. 搭載されているFPGA はArtix-7(AMD社, 旧ザイリンクス)です. 開発ツ ールはAMD社のVivadoになります.

#### 今回やること

FPGAには、自由に構成できるロジック回路(LUT)とは別に、専用のメモリ・ブロックが内蔵されています。FPGA内部信号表示IPのうち、フォント・データを格納するROM(フォントROM)や信号名を格納するROM(信号ラベルROM)は、このメモリ・ブロックを利用する方法もあります。

今回は、そのROMデータの作成方法と、メモリ・ブロックを利用したIP化を行う場合のFPGA開発ツールの設定方法、外部モニタ表示回路を動かすのに必要なクロック生成IPの設定方法について説明します。

写真1 FPGA内部信号 VGA表示IP は Artix-7 搭載ボード Cmod A7-35Tに実装してみる

今回は、Verilog記述ではなくFPGAメーカが用意した機能でROMデータIPやクロック発生IPを生成する

### ROM データを IP 化する手順その 1 ···· 元データ・ファイルの準備

■ 開発ツールに読み込ませるROMデータ・ファイルの準備をしておく

フォントや信号ラベルの情報は、FPGA内に用意されたメモリ・ブロックを使って構成するとして、開発ツールに合わせたROMデータのファイルを準備する必要があります。そのファイルの作り方を解説します。

フォントROMや信号ラベルROMを生成する際の元となるファイルや生成ツールは、サポート・サイトに掲載、あるいは本誌サイトからのダウンロード・ファイルに同梱します。何もない状態から作成する必要はありません。

#### ● AMD社向けROMファイルの拡張子はcoe

coeファイル(coefficient)はAMD社(旧ザイリンクス社)のデバイス用の初期化ファイルです。表記基数の定義と、それに続いた初期化データ(ベクタ)で構成されるテキスト・ファイルです。

基数は2,10,16進数から選択でき、各ベクタはコンマで区切り、最後はセミコロンで終了します.

coeファイルの詳細は以下のWebサイトを参照してください. ここでは最低限必要な項目のみ説明します.

- ▶ https://docs.xilinx.com/r/2022.1 日本語/ug896 vivado ip/COE ファイル例

- フォントROM用coeファイルのフォーマット

フォント ROM 用の coe ファイル (Font\_ROM.coe) の主要部を**リスト1**に示します.

最初の行はコメント行です.この行に限らずセミコロンの後のテキストはコメントとして無視されます.

2行目の文は初期化データが2進数表記であること を規定しています.

3行目の文は初期化データ開始の意味があります. 空行を挟んで 00000000 という文字列が8行並んでいます. このひとかたまりが1文字分のフォント・デー