編集部

2021年3月号 特集サポート

FPGA開発ツールの使い方

~ザイリンクス製FPGAを使う場合~

FPGA開発ツール“Vivado”のセットアップ

●アカウント取得

初めてザイリンク社のツールを使う場合は、アカウントの登録が必要です。ザイリンクス社のWebサイトにアクセスし、右上にある人間型のアイコンをクリックすると、「ログイン|登録」の選択が出てくるので、これをクリックします。

図1 ザイリンク社のWebサイトの右上

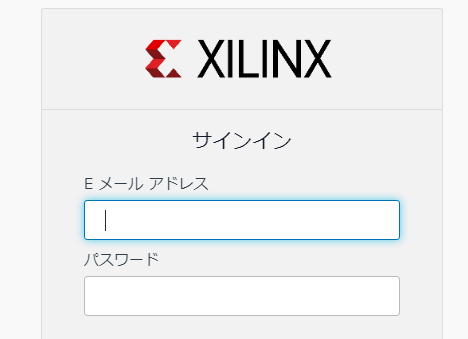

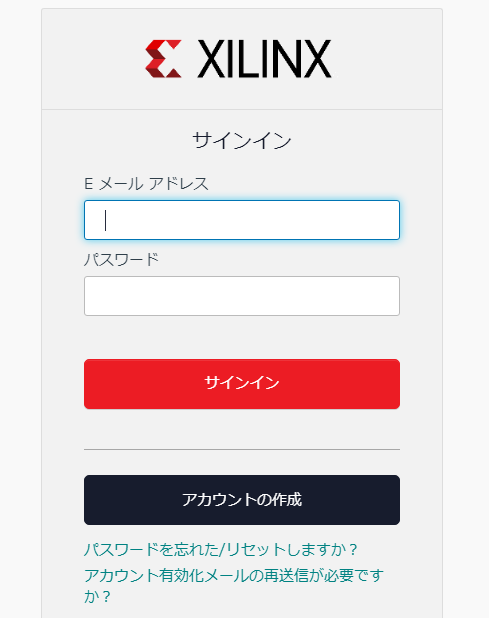

すでにアカウントをお持ちの場合は、登録したメールアドレスとパスワードを入力して「サインイン」してください。アカウントを作成する場合は、登録するメールアドレスを入力し、「アカウントの作成」をクリックします。

図2 ザイリンク社のサインイン画面

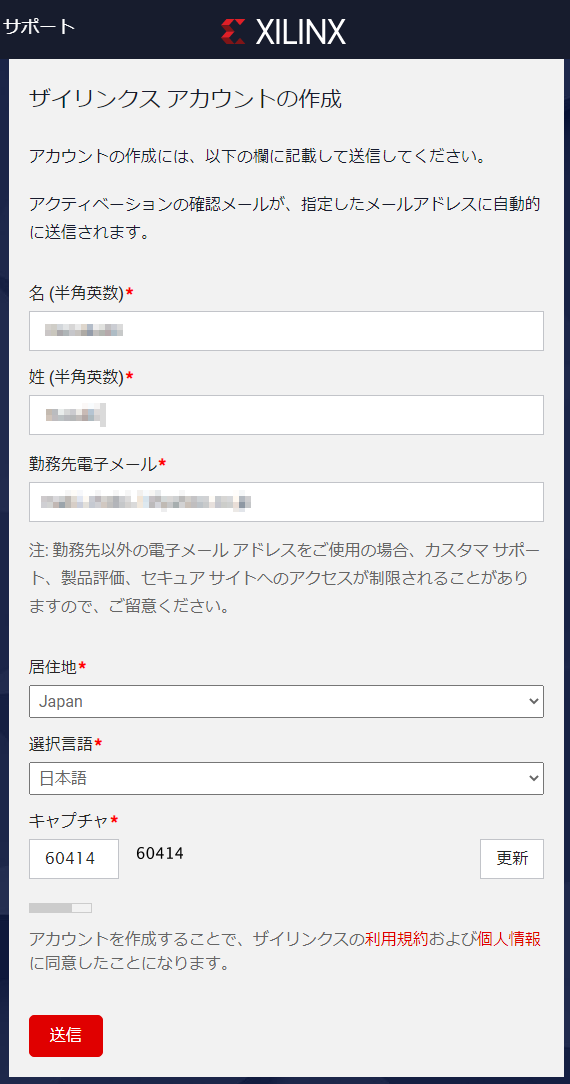

アカウントの作成画面では、名前や居住地などの項目を入力します。キャプチャには右側に表示されている英数字を入力します(ボット対策のための入力)。入力を完了したら「送信」をクリックします。

図3 アカウントの作成画面

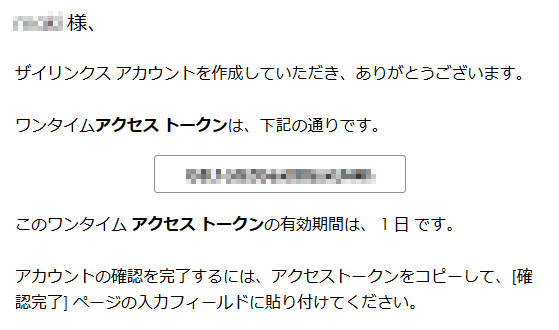

すると登録したメールアドレスにアクセストークンが送られてくるので、この文字列をコピーしておきます。

図4 送られてきたアクセストークン

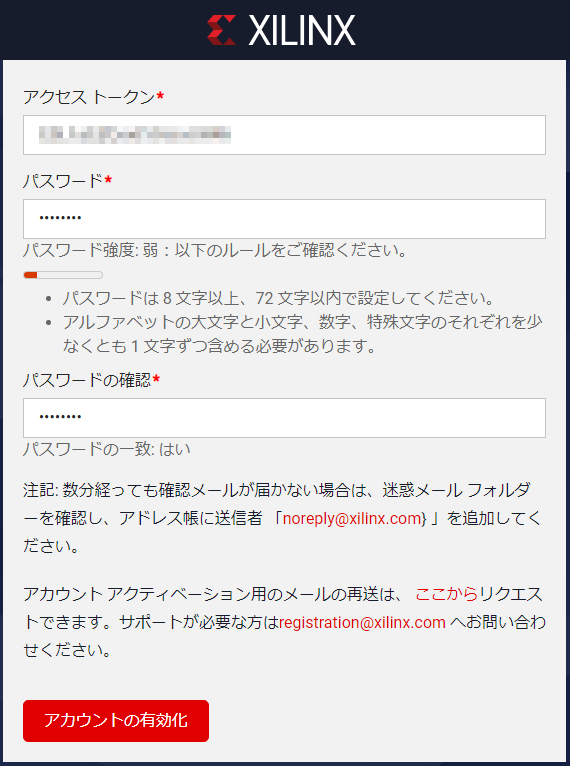

アカウント取得画面ではアクセストークンの入力待ちになっているので、ここにアクセストークンとサインイン時のパスワードを設定します。パスワードは大文字小文字各最低1文字、さらに数字と記号を最低1文字含み、最低8文字が必要です。設定が完了したら「アカウントの有効化」をクリックします。

図5 アカウントの有効化

アカウントが有効化されると、Webページは図2のサインイン画面に切り替わるので、登録したメールアドレスとパスワードでサインインします。

●ダウンロード

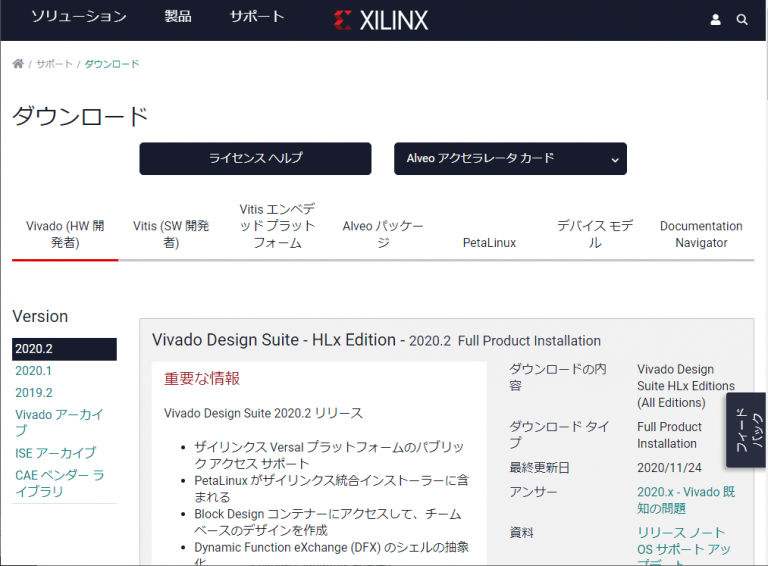

Vivadoは、Vivadoのダウンロード・ページからダウンロードできます。

図6 Vivadoのダウンロード・ページ

画面をスクロールしていくと、ダウンロードするファイルの選択ができます。すべてをダウンロードすると巨大なファイル・サイズとなるので、使用するOSに合わせて「自己解凍型ウェブ インストーラー」を選択して実行してください。

図7 ウェブ インストーラーを選択

ダウンロード時に名前や会社名の入力画面になることがあるので、改めて入力してください。

●インストール

ネットワーク経由でダウンロードしながらのインストールになるので、ネットに接続できる環境である必要があります。

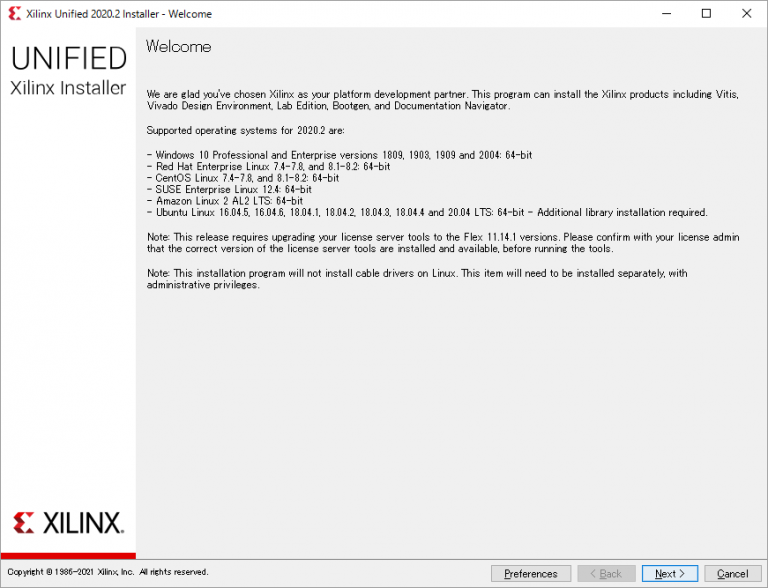

ダウンロードしたファイルを実行してインストールを開始します。スプラッシュ画面が表示された後、しばらくすると下記のようなインストール開始画面になります。

図8 インストール開始画面

インストールは基本的に「Next」をクリックしてインストールを進めればOKです。途中、アカウントの確認画面が出てくるので、登録したメールアドレスとパスワードを入力します。

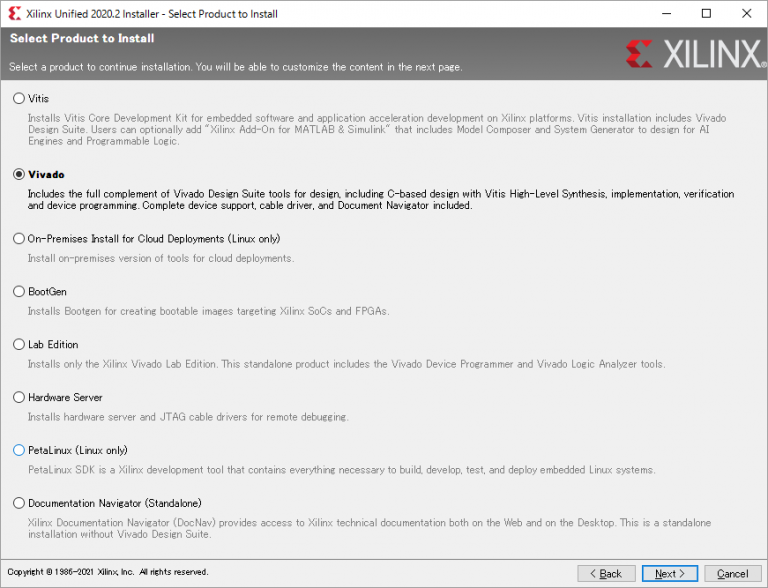

次の画面では「Vavdo」を選択して「Next>」をクリックします。

なお、将来的にZynqシリーズやソフトマクロCPUコアMicroBlazeを使う場合は、一番上の「Vitis」をインストールしてください(Vivadoも同時にインストールされる)

図9 Vavdoを選択

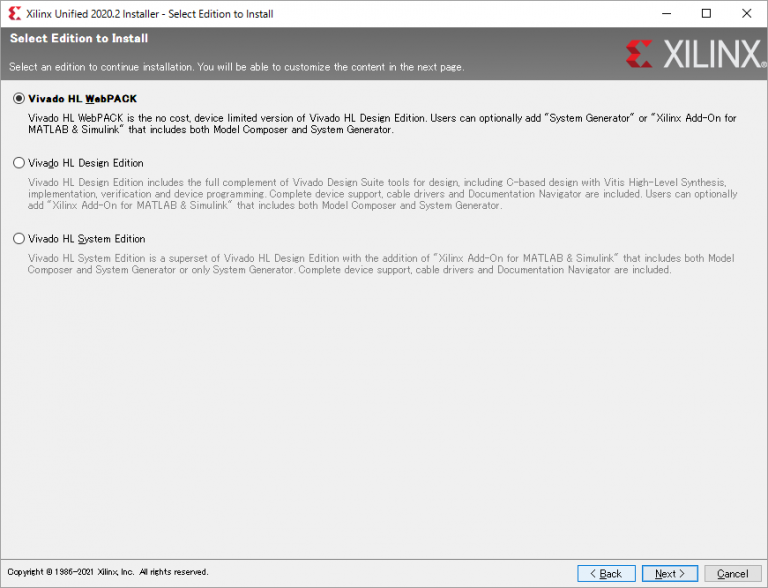

次の画面では「Vivado HL WebPACK」を選択して「Next>」をクリックします。

またライセンス契約(Accept License Agreements)の確認画面では「I Agree」を選択してクリックします。

図10 Vivado HL WebPACKを選択

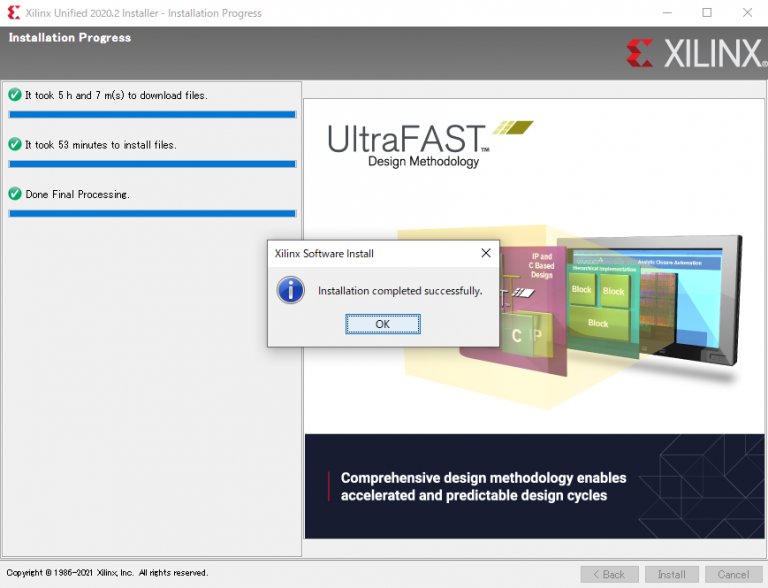

ウェブインストーラーなので、ツール本体のダウンロードから始まります。全部で10G~20Gバイト程度のファイルをダウンロードします。それが完了してからインストールを開始するので、作業時にトータルで50Gバイト前後の空き容量が必要になります。インストールの完了まで、数時間程度かかるでしょう。

インストールが完了すると、下記のような画面が表示されます(途中ドライバのインストールが行われる場合がありますが、キャンセルして後から実行してもかまいません)。

図11 インストール完了

●インストール手順説明書

詳細なインストール手順は下記PDFに説明があります。参考にしてください。

→ インストール手順PDF

FPGA開発ツール“Vivado”の使い方

●プロジェクト作成前に…

本特設ページからダウンロードしたファイルを解凍した後に生成される「BASYS3」フォルダを任意のディレクトリにコピーしておきます。ここでは例として、D:\FPGA内にコピーするものとします。

●プロジェクトの作成

まずはインストールしたVivadoを起動します。

図12 Vivadoの起動

「Create Project」をクリックするとプロジェクト作成のウィザードが開始されます。

図13 Vivadoのプロジェクト作成開始

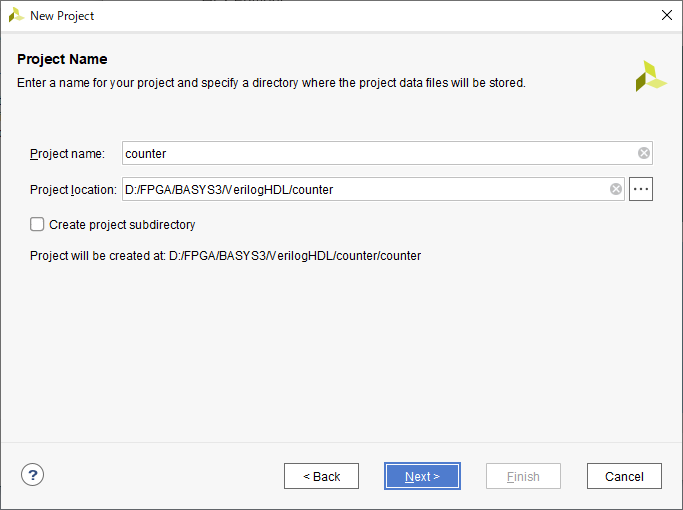

プロジェクト作成は、後でも設定できる項目も多いので基本的に「Next>」を選択していけば問題ありません。下記の画面ではプロジェクトの名前を設定します。ここでは例として、本誌特集サンプル・ソースをコピーしたフォルダ(D:\FPGA\BASYS3\VerilogHDL\counter)に、プロジェクトを作成してみることにします。

下図のように、ディレクトリ名を、D:/FPGA/BASYS3/VerilogHDL/counter(VHDLを使う場合はD:/FPGA/BASYS3/VHDL/counter)に、プロジェクト名をcounterとして、「Next>」をクリックします。

(「Create project subdirectory」のチェックを外すと、指定したフォルダにプロジェクトが作成されます)

図14 プロジェクト名の設定

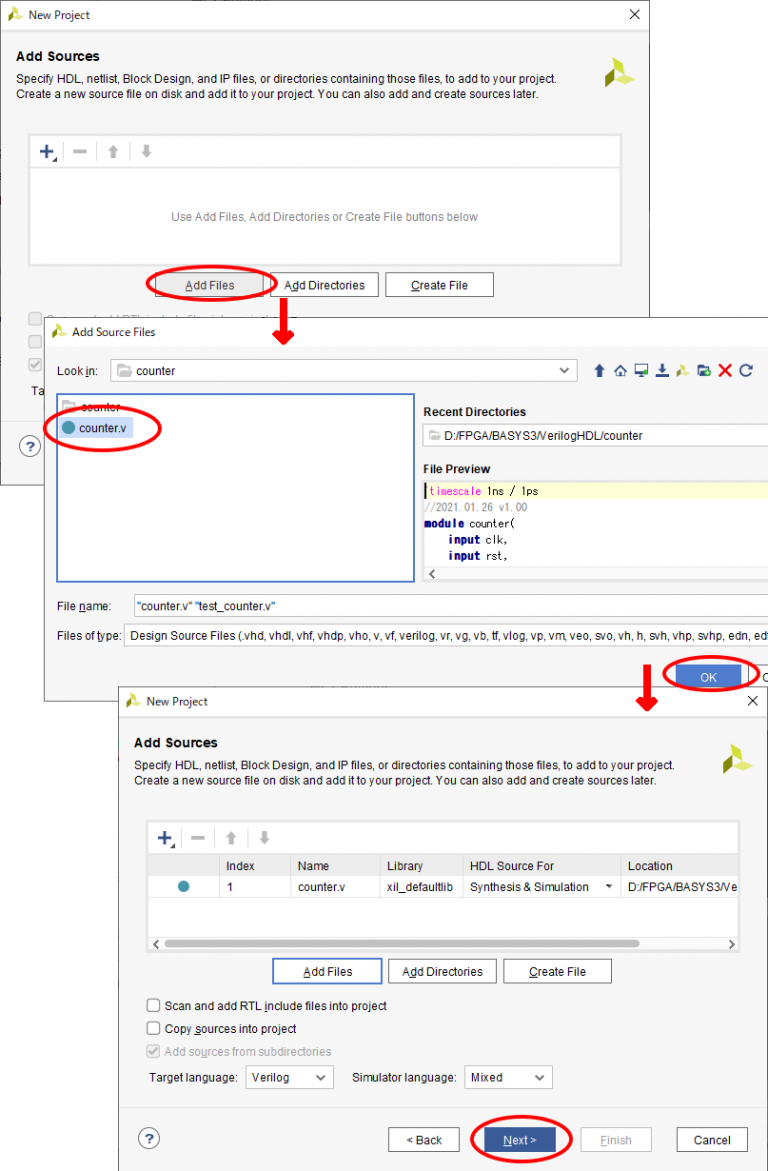

次にHDLソースを読み込みます。「Add Fils」をクリックして開いたウィンドウで、読み込むHDLソースを選択して「OK」をクリックします。HDLソースがプロジェクトに取り込まれたのを確認したら、「Next>」をクリックします。

図15 HDLソースの読み込み

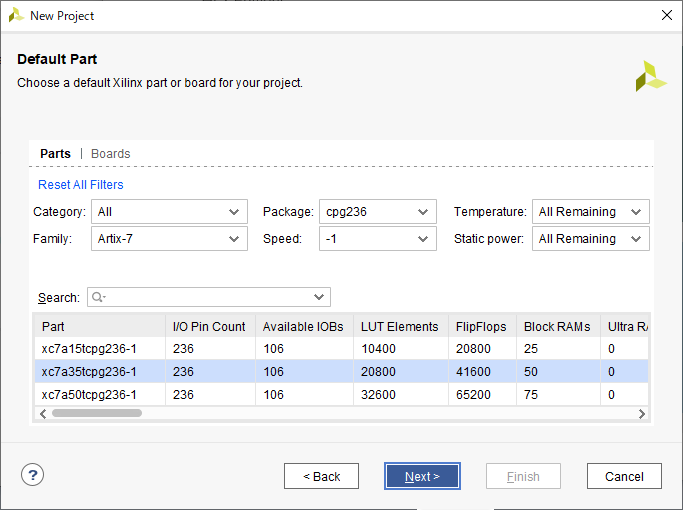

デバイス選択画面では、ファミリに「Artix-7」を、パッケージに「CPG236」を、スピードグレードに「1]を選択し、使用するFPGA評価ボードBASYS3に搭載されている「XC7A35CPG236-1」が絞られるので、これを選択します。

後は「Next」を選択していけば、プロジェクト作成の終了です。

図16 デバイスの設定

●ソースコード作成とアナライズ

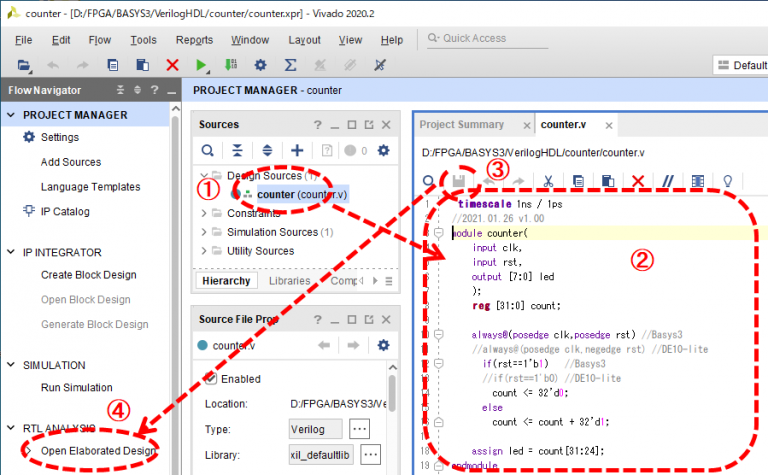

HDLソース(counter.vなど)をダブルクリックするとエディタが起動するので、内容を編集し保存します。次に「Open Elaborated Design」をダブルクリックするとアナライズが実行されます。文法のエラーなどがあれば、ここでエラーが表示されます。

図17 ソースコード作成とアナライズ

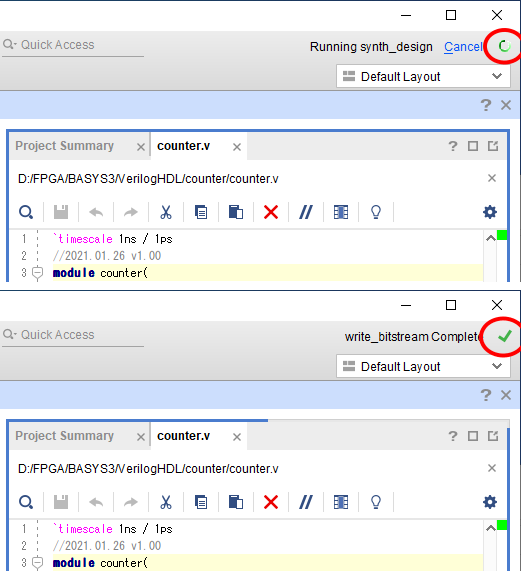

また、アナライズや論理合成など、ツールが時間のかかる処理をしているときは、右上に下記のように「Runing 〇〇〇」と表示され、アイコンが回転するアニメーションをしています。処理が完了すると、チェックマークのアイコンに変わります。

図18 ツールが処理中/完了時の表示

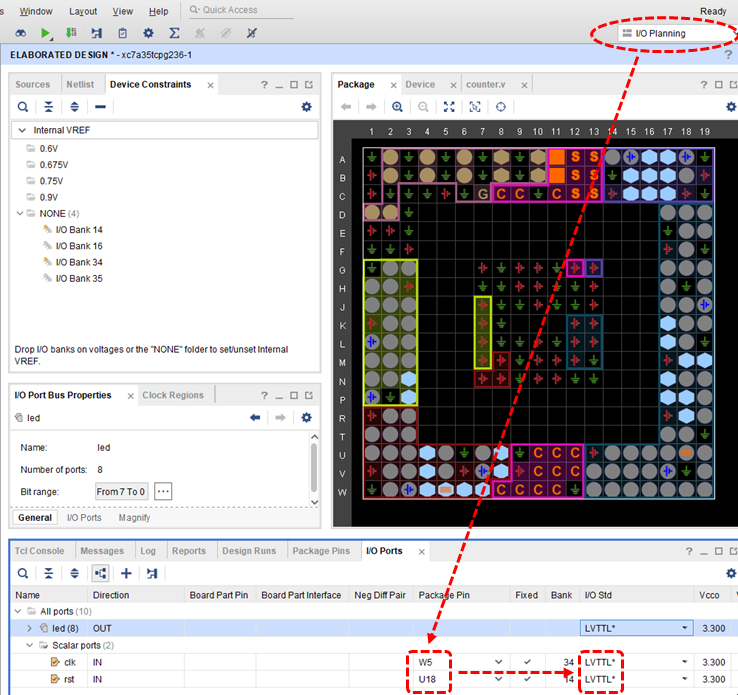

●ViVadoのピン配置指定

HDLソースの入力が終わったら、「ELABORATED DESIGN」で「I/O Plannign」を選択し、信号ごとにピン配置(PackagePin)と信号レベル(I/O Std)を指定します。

図19 ViVadoのピン配置指定

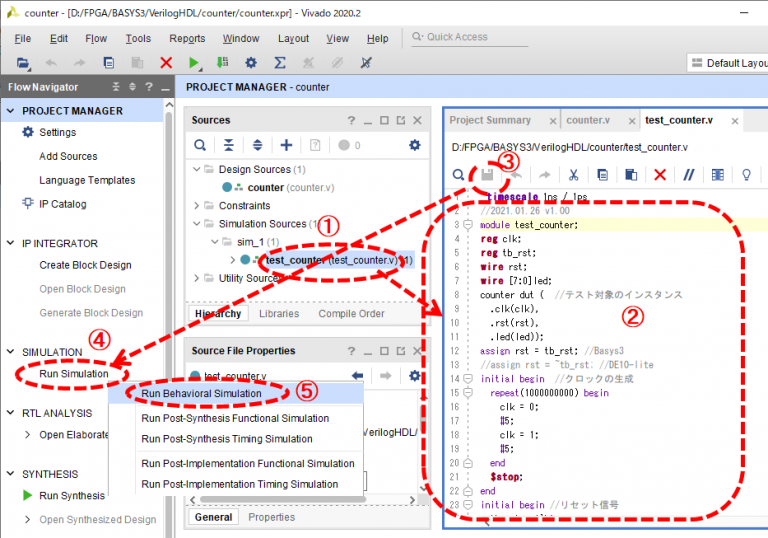

●Vivadoのシミュレーション実行

メニュー・バー「File」→「Add Source」または「Flow Navigator」の「PROJECT MANAGER」の「Add Source」をクリックすると、ファイル追加・作成ウィンドウが開きます。ここで「Add or create simulation sources」を選ぶと、図15のようにファイル選択ウィンドウが出るので、テストベンチ(test_counter.v、VHDLを使う場合はtest_counter.vhd)を選択します。すると下記画面のようにSimulation Sourcesにテストベンチが追加されるので、これをダブルクリックしてテキスト・エディタ画面で編集できます。編集後、ファイルを保存し、「Run simulation」→「Run Behavioral Simulation」でシミュレーションが実行されます。

図20 Vivadoのシミュレーション実行

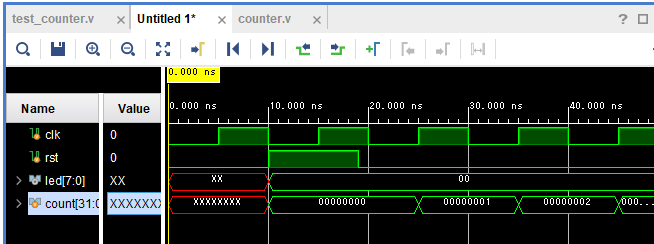

リセット解除後にクロックが立ち上がると、countがインクリメントされるのがわかります。

図21 Vivadoのシミュレーション波形

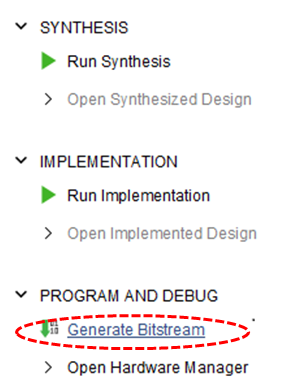

●論理合成・配置配線・FPGAデータ生成

「Flow Navigator」の「PROGRAM AND DEBUG」の「Generate Bitstream」(FPGA書込みデータ生成の実行)をクリックすると、Run Synthesis(論理合成)と、Run Implementation(配置配線)が実行されます。ツール内ではタイムスタンプを確認し、前工程でなにか変更があれば、後工程もすべて再実行されます。つまり、HDLソースを変更すると、全体が再実行されます。

図22 論理合成・配置配線・FPGAデータ生成

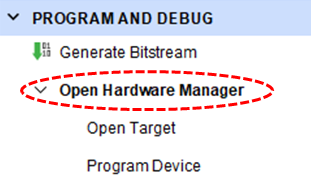

●VivadoのFPGAへの書込み

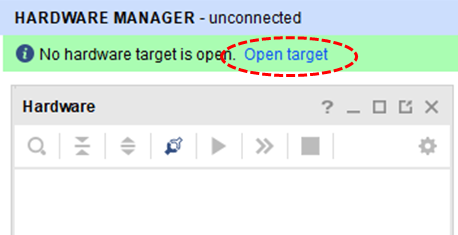

「Open Hardware Manager」をダブルクリックすると、HARDWARE MANAGERが起動します。

図23 HARDWARE MANAGERが起動

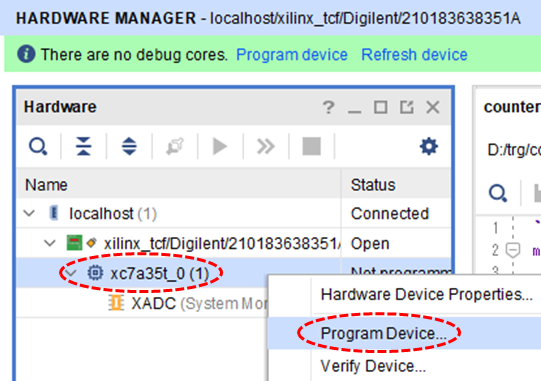

「Open Target」をダブルクリックするとJTAG経由で接続されているFPGAを検索します。

図24 接続されているFPGAを検索

ターゲットとなるFPGA(BASYS3ではxc7a35t_0)上でマウス右ボタンをクリックし、「Program Device」を選択します。表示されたウィンドにしがってFPGAへ書き込みします。

図25 FPGAへの書込み